## Positive and Negative Logic

Boolean values (zero and one) represent physical quantities such as voltage or state of an entity (door is open, light is off).

Assigning "1" to high value, and "0" to low value is called positive logic, and assigning "0" to high value, and "1" to low value is called negative logic.

## Example:

Function table of a physical device with 2 inputs and one output is shown below.

If we use the positive logic, the device can be implemented with an AND gate.

In negative logic system, the device is implemented with an OR gate.

| Physical Device                                                                               |     |      |         |   | Positive Logic |      |      |     | Negative Logic |      |        |   |

|-----------------------------------------------------------------------------------------------|-----|------|---------|---|----------------|------|------|-----|----------------|------|--------|---|

|                                                                                               | Inp | uts: | Output: |   | Inp            | uts: | Outp | ut: | Inp            | uts: | Output | : |

|                                                                                               | ×1  | x2   | z       | , | ×1             | x2   | Z    |     | ×1             | x2   | Z      |   |

|                                                                                               | L   | L    | L       | ( | )              | 0    | 0    |     | 1              | 1    | 1      |   |

|                                                                                               | L   | Н    | L       | ( | )              | 1    | 0    |     | 1              | 0    | 1      |   |

|                                                                                               | Н   | L    | L       |   | 1              | 0    | 0    |     | 0              | 1    | 1      |   |

|                                                                                               | Н   | Н    | Н       |   | 1              | 1    | 1    |     | 0              | 0    | 0      |   |

| http://docadess:ite.orde.te/confluence/                                                       |     |      |         |   |                |      |      |     |                |      |        |   |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011 - 2022 Feza BUZLUCA 3.5 |     |      |         |   |                |      | .5   |     |                |      |        |   |

Digital Circuits License: <a href="https://creativecommons.org/licenses/by-nc-nd/4.0/">https://creativecommons.org/licenses/by-nc-nd/4.0/</a>

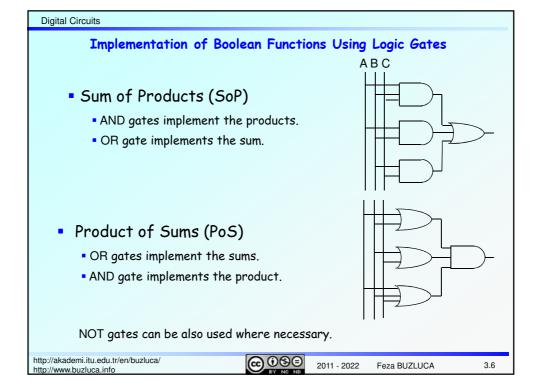

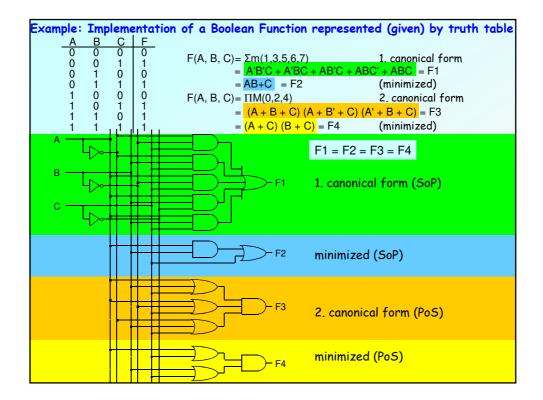

#### Implementation of Boolean Functions Using Logic Gates (cont'd)

There are many ways to express a Boolean function. We implement each one using different logic gates.

**Example:**  $Z = A' \cdot B' \cdot (C + D) = (A' \cdot (B' \cdot (C + D)))$  (Associative Law)

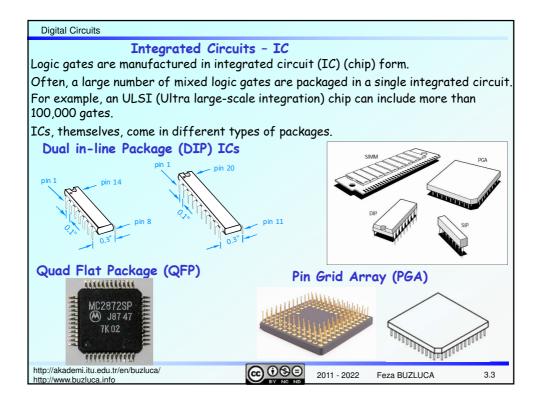

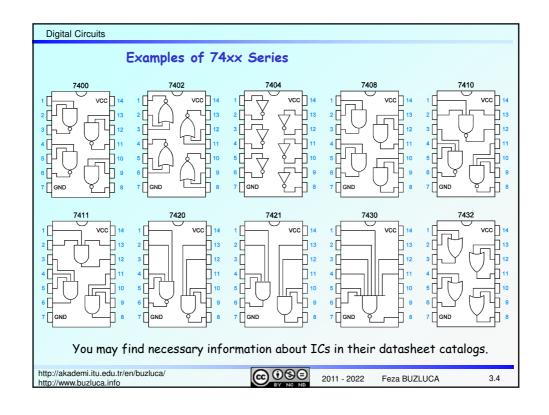

Sometimes, it is necessary to manipulate logic expressions of functions based on the types of available gates (for example, if we have only 2-input AND gates). Reduction of logic equations is still necessary in order to fit the equations into a small number of  ${\sf ICs}$ .

# Functionally Complete Sets of Logic Gates

A set of logic operations is said to be **functionally complete**, if any Boolean function can be expressed using only this set of operations.

- The set {AND, OR, NOT} is obviously functionally complete because AND, OR, and NOT are main operations that are defined in of the Boolean algebra.

Any function can be expressed in sum-of-products (or product-of-sums) form, and a sum-of-products expression uses only the AND, OR, and NOT operations.

- Since the set of operations {AND, OR, NOT} is functionally complete, any set of logic gates which can realize {AND, OR, NOT} is also functionally complete.

- For example, {AND, NOT} is also a functionally complete set of gates because OR can be realized using only AND and NOT.

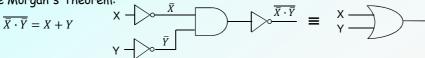

To prove it we can use De Morgan's theorem.

De Morgan's Theorem:

Since {AND, NOT} is functionally complete, we can express any Boolean function using only AND and NOT.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2022

Feza BUZLUCA

3.9

Digital Circuits

#### Universal Logic Gates

If a single gate forms a functionally complete set by itself, then any Boolean function can be realized using only gates of that type.

This type of a gate is called universal logic gate.

- The NAND gate is an example of such a gate.

Remember: the NAND gate performs the AND operation followed by inversion (AND-NOT).

- NOT, AND, and OR can be realized using only NAND gates.

- Thus, any Boolean function can be realized using only NAND gates.

- Similarly, the set consisting only of the binary operator NOR is also functionally complete.

- All other logic functions can be realized using only NOR gates.

NAND (and also NOR) gates are called universal logic gates.

# Proof of functional completeness

To prove that NAND and NOR operators are functionally complete, we have to show that AND, OR, NOT operations can be implemented using only NAND (or alternatively, NOR) gates.

NAND is denoted by symbol |

NOR is denoted by symbol  $\downarrow$

| AND: $x \cdot y = ((x \cdot y)')'$ Involution $x \cdot y = (x' + y')'$ de Morgan $= (x' \downarrow y)'$ OB: $x + y = (x' \cdot y')'$ de Morgan $x + y = ((x + y)')'$ Involution |      | NAND                                        | NOR                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------|-----------------------------------------------------|

| AND: $x \cdot y = ((x \cdot y))$ Involution $= (x' \downarrow y')$ OB: $x + y = (x' \cdot y')'$ de Morgan $x + y = ((x + y)')'$ Involution                                      | NOT: | = (x·x)' x — b—x'                           | = (x+x)' x - o x'                                   |

| (In) ((1.1)) ((1.1))                                                                                                                                                            | AND: | * * * * * * * * * * * * * * * * * * * *     |                                                     |

| - (x \ y)                                                                                                                                                                       | OR:  | x+y = (x'·y')' de Morgan<br>x+y = (x'   y') | x+y = ((x+y)')' Involution<br>= $(x \downarrow y)'$ |

**Digital Circuits**

http://www.buzluca.info

## Relation between NAND and NOR

- NAND NOR Conversions

- de Morgan:

1.

$$A' \cdot B' = (A + B)'$$

2.

$$A' + B' = (A \cdot B)'$$

3.

$$(A' \cdot B')' = A + B$$

4.

$$(A' + B')' = (A \cdot B)$$

- These expressions show that,

- 1. An AND gate with inverted inputs is the equivalent of the NOR gate.

- 2. An OR gate with inverted inputs is the equivalent of the NAND gate.

- 3. A NAND gate with inverted inputs is the equivalent of the OR gate.

- 4. A NOR gate with inverted inputs is the equivalent of the AND gate.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

# Implementation of Boolean functions using only NAND (NOR) gates

There are four different combinations:

- 1. Expression in SOP form, implementation using NAND gates

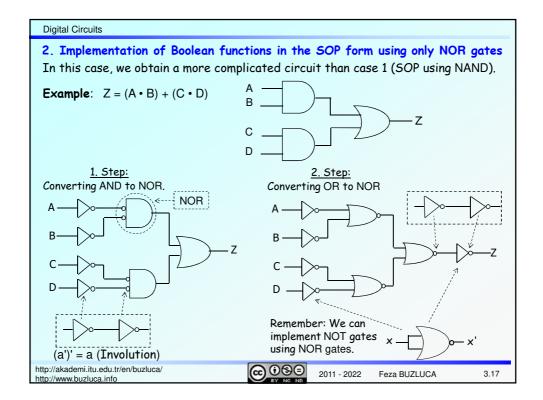

- 2. Expression in SOP form, implementation using NOR gates

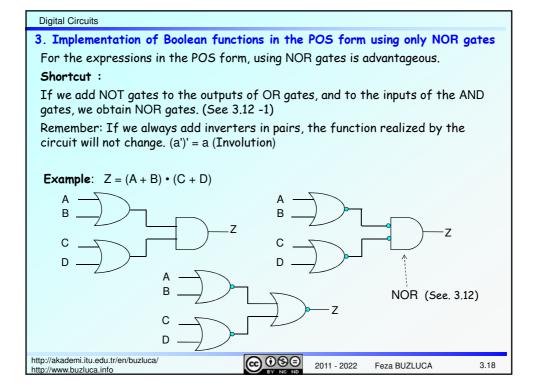

- 3. Expression in POS form, implementation using NOR gates

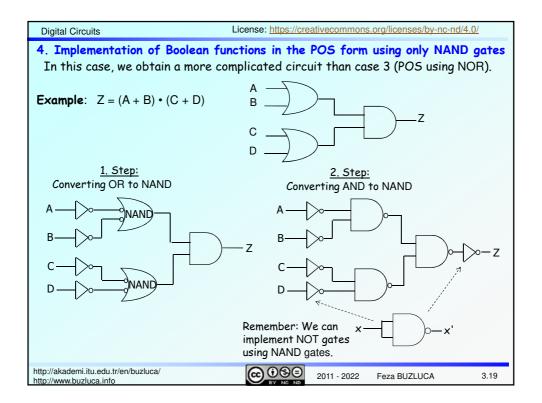

- 4. Expression in POS form, implementation using NAND gates

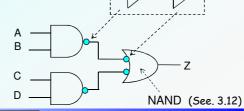

# 1.Implementation of Boolean functions in the SOP form using only NAND gates

**Shortcut:** If we add NOT gates to the outputs of AND gates and to the inputs of the OR gates, we obtain NAND gates. (See 3.12 - 2)

If we always add inverters in pairs (NOT-NOT), the function realized by the circuit will not change. (a')' = a (Involution)

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info 2011 - 2022

Feza BUZLUCA

3.13

#### Digital Circuits

# Example (cont'd):

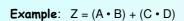

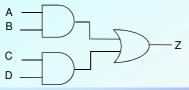

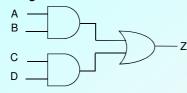

# Solution using algebraic conversion:

Expression is inverted twice. (Z')' = Z (Involution)

$$Z = (A \cdot B) + (C \cdot D)$$

$$= [((A \cdot B) + (C \cdot D))']$$

(SoP form)

(De Morgan)

$= [(A \cdot B)' \cdot (C \cdot D)']'$  $= (A \mid B) \mid (C \mid D)$

(only NAND gates)

# Algebraic verification:

$$Z = [ (A \cdot B)' \cdot (C \cdot D)' ]'$$

Expression using NANDs (circuit on the right)

$$= [ (A' + B') \cdot (C' + D') ]'$$

$$= [ (A' + B')' + (C' + D')' ]$$

Expression of the circuit on left

http://akademi.itu.edu.tr/en/buzluca/http://www.buzluca.info

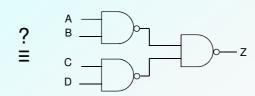

# Implementation using gates with limited number of inputs

Sometimes, it is necessary to implement products (or sums) with many literals using gates that accept only 2 inputs (remember the integrated circuits in 3.4).

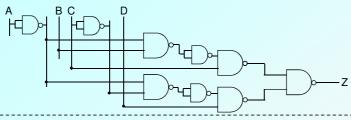

# Example:

$Z = \overline{A}BC + \overline{A}\overline{C}D$

Implement this expression using only 2-input NAND Gates.

#### Solution 1:

1. Implementation with the classical gates of the Boolean algebra

2. Inserting NOT gates to obtain NAND gates

http://akademi.itu.edu.tr/en/buzluca/http://www.buzluca.info

2011 - 2022

Feza BUZLUCA

3.15

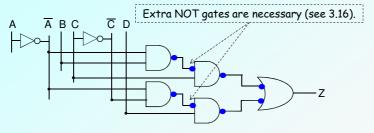

# Example (cont'd): Solution 1:

**Digital Circuits**

3. Implementation with 2-input NAND gates

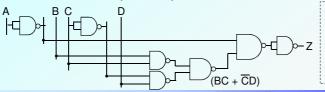

## Solution 2:

Manipulating the original expression to obtain a simpler circuit

$$Z = \overline{A}BC + \overline{A}\overline{C}D = \overline{A}(BC + \overline{C}D)$$

The circuit in solution 2 is cheaper to implement than the circuit in solution 1.

Therefore solution 2 is preferable to solution 1.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info @ 0 8 9

2011 - 2022

Feza BUZLUCA

3.16