| Digital Circuits License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design of Clocked Synchronous Sequential Circuits                                                                                                                           |

| The design of a sequential circuit starts with the problem statement which specifies the desired relationship between the input and output sequences (scenario).            |

| The process of designing a circuit to perform a given logical function is quite similar to the process of designing a computer program to perform a given task.             |

| First, we should describe and appropriately model the real-world problem.                                                                                                   |

| Then, we should design a circuit to solve the problem.                                                                                                                      |

| Designing a sequential circuit consists of the following steps:                                                                                                             |

| 1. We describe the problem ( <b>functional requirements</b> of the circuit) verbally. We can use timing diagrams to avoid uncertainties.                                    |

| 2. We decide which design model (Mealy/Moore) would better represent the circuit.                                                                                           |

| 3. We determine the <b>states</b> that will make up the finite state machine (FSM).                                                                                         |

| a) We determine the state transitions based on the inputs and current states.                                                                                               |

| <ul> <li>b) We construct the state transition and output tables. We can use a state diagram if<br/>it makes the design easier.</li> </ul>                                   |

| c) We reduce the number of states in the state table (if applicable). The purpose is to<br>build a correctly functioning machine with the fewest possible number of states. |

| d) This process is similar to the process of designing a computer program; that is why it requires an intuitional approach.                                                 |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011 - 2023 Feza BUZLUCA 10.1                                                                              |

| Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Steps of sequential circuit design (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4. Assigning codes to each state: A binary code is assigned to each state. If<br>there are n states, the number of variables (number of flip-flops) m is<br>computed as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $m = \lceil \log_2 n \rceil$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| where $\lceil x \rceil$ denotes the ceiling function. For example, $\lceil 4.1 \rceil = 5$ and $\lceil 4.0 \rceil = 4$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ol><li>We construct the state transition and output table based on the values of<br/>the state variables.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| <ol><li>We decide what type of flip-flops we will use.</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ol> <li>Using the transition table for the selected flip-flop type, we determine the<br/>inputs of the flip-flops. We obtain the <b>function (F)</b> that drives the flip-<br/>flops.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

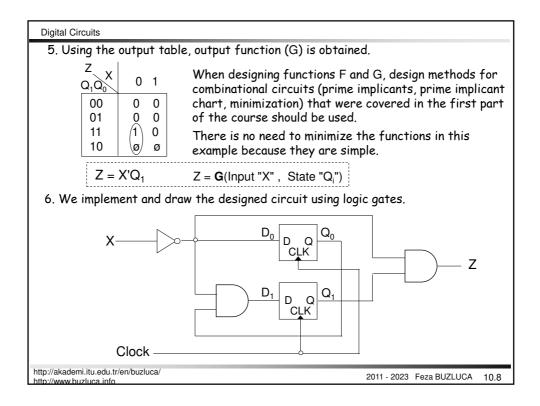

| 8. From the output table, we obtain the <b>output function (G)</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9. We design <b>combinational circuits for the functions</b> (F and G) and implement each with the minimum cost.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| http://akademi.itu.edu.tr/en/buzluca/ 2011 - 2023 Feza BUZLUCA 10.2 http://www.buzluca.info 2011 - 2023 Feza BUZLUCA 2012 Feza 2 |

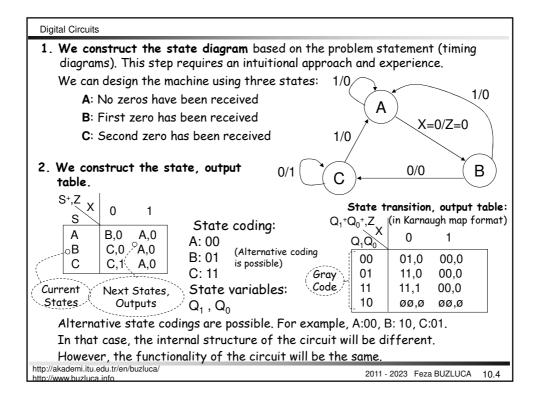

| Digital Circu                                                                                                                                                       | Digital Circuits |            |                                                                                                                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

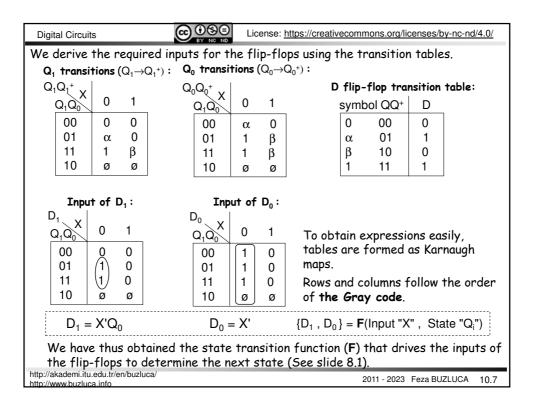

| 4. We d                                                                                                                                                             | letermi          | ne the     | input functions of the flip-flops:                                                                                                                     |  |  |  |

| We w                                                                                                                                                                | vill use         | D flip-    | flops in this example.                                                                                                                                 |  |  |  |

| In thi                                                                                                                                                              | s step,          | we wil     | step, we determined transitions for all flip-flops.<br>I investigate the values that must be applied to the inputs of<br>uke the required transitions. |  |  |  |

| We wi                                                                                                                                                               | ill use t        | he tra     | nsition table of the flip-flop for this purpose.                                                                                                       |  |  |  |

| D flip                                                                                                                                                              | o-flop           | transit    | ion table:                                                                                                                                             |  |  |  |

| symbo                                                                                                                                                               | l QQ+            | D          |                                                                                                                                                        |  |  |  |

| 0<br>α                                                                                                                                                              | 00<br>01         | 0          | This table shows the value that must be applied to the input of a D flip-flop for a given transition.                                                  |  |  |  |

| β<br>1                                                                                                                                                              | 10<br>11         | 0          | Different types of flip-flops have different transition tables.                                                                                        |  |  |  |

| The transition table of the D flip-flop is simple. The value that must be applied to the input of the D flip-flop is equal to the next value of its state variable. |                  |            |                                                                                                                                                        |  |  |  |

| http://akademi.i<br>http://www.buzlu                                                                                                                                |                  | 1/buzluca/ | 2011 - 2023 Feza BUZLUCA 10.6                                                                                                                          |  |  |  |

Digital Circuits

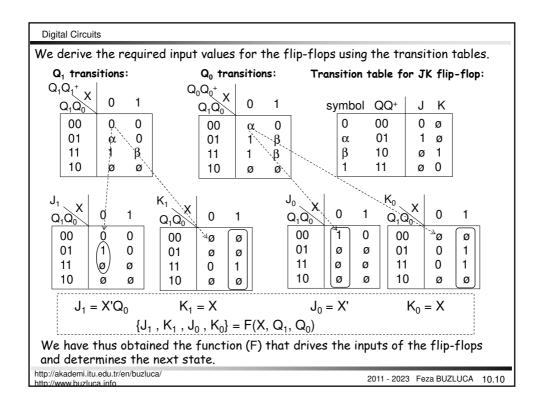

Example: Same circuit designed using J-K flip-flops

The first three steps are the same.

4. In this example, we will use positive edge-triggered J-K flip-flops.

J-K flip-flop transition table:

| ymbol | QQ+    | J            | Κ                                                                                            |                                  |

|-------|--------|--------------|----------------------------------------------------------------------------------------------|----------------------------------|

| 0     | 00     | 0            | ø                                                                                            |                                  |

| α     | 01     | 1            | ø                                                                                            |                                  |

| β     | 10     | ø            | 1                                                                                            |                                  |

| 1     | 11     | ø            | 0                                                                                            |                                  |

|       | 0<br>α | α 01<br>β 10 | $\begin{array}{c ccccc} 0 & 00 & 0 \\ \alpha & 01 & 1 \\ \beta & 10 & \emptyset \end{array}$ | 0 00 0 ø<br>α 01 1 ø<br>β 10 ø 1 |

Using J-K flip-flops instead of D flip-flops generally yields simpler logic functions for the next state. However, since the functions in this example are already simple, the J-K flip-flop yields no further simplification.

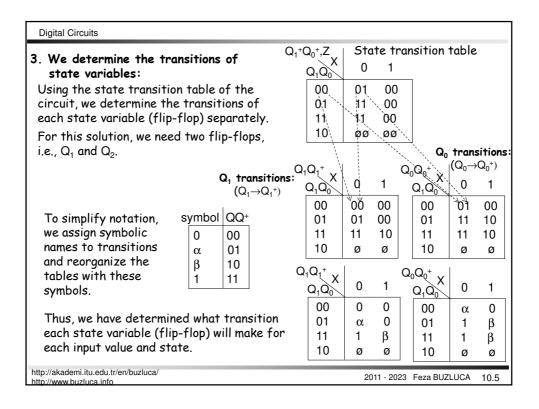

We had determined the transitions of state variables from the state transition table in step 3.  $\Omega_1$  transitions  $(\Omega_1 \rightarrow \Omega_1^+)$ :  $\Omega_2$  transitions  $(\Omega_2 \rightarrow \Omega_2^+)$ :

|                                  | _         |      |      | <b>Q</b> 1 | Transitio   | ons (C | J1→Q1 | ,*): <b>U</b> ( | ) Trans         | SITIONS  | $(Q_0 \rightarrow$ | $Q_0^{+}$ |

|----------------------------------|-----------|------|------|------------|-------------|--------|-------|-----------------|-----------------|----------|--------------------|-----------|

| Q <sub>1</sub> +Q <sub>0</sub> + | ⁺,Z       |      |      | C          | $Q_1 Q_1^+$ |        |       | Q               | Q0 <sup>+</sup> | .        |                    |           |

| Q                                |           | 0    | 1    |            | $Q_1 Q_0$   | 0      | 1     |                 | $Q_1 Q_0$       | 0        | 1                  |           |

| (                                | 00        | 01,0 | 00,0 |            | 00          | 0      | 0     |                 | 00              | α        | 0                  |           |

| (                                | 01        | 11,0 | 00,0 |            | 01          | α      | 0     |                 | 01              | 1        | β                  |           |

| · ·                              | 11        | 11,1 | 00,0 |            | 11          | 1      | β     |                 | 11              | 1        | β                  |           |

|                                  | 10        | øø,ø | øø,ø |            | 10          | ø      | ø     |                 | 10              | ø        | ø                  |           |

| http://akader<br>http://www.bi   |           |      | ıca/ |            |             |        |       | 2011            | - 2023          | Feza BUZ | LUCA               | 10.9      |

| 11110.// 11111.01                | uziuou.ii | lio  |      |            |             |        |       |                 |                 |          |                    |           |

| Digital Circu                         | iits                              |                      |                  |                  |               |           |                  |                      |             |                  |                 |

|---------------------------------------|-----------------------------------|----------------------|------------------|------------------|---------------|-----------|------------------|----------------------|-------------|------------------|-----------------|

| Transit                               | Transition tables for flip-flops: |                      |                  |                  |               |           |                  |                      |             |                  |                 |

| Transiti                              | on ta                             | ables fo             | or di            | ffer             | ent types of  | flip-flop | os are           | e given b            | belov       | v.               |                 |

| Trans                                 | itior                             | n table              | e for            | S-F              | R flip-flop : | Trans     | ition            | table <sup>.</sup>   | for         | J-K              | flip-flop :     |

| syr                                   | nbol                              | QQ⁺                  | S                | R                |               | sy        | mbo              | I QQ⁺                | J           | κ                |                 |

|                                       | 0<br>α<br>β<br>1                  | 00<br>01<br>10<br>11 | 0<br>1<br>0<br>ø | ø<br>0<br>1<br>0 |               |           | 0<br>α<br>β<br>1 | 00<br>01<br>10<br>11 | 0<br>1<br>Ø | ø<br>ø<br>1<br>0 |                 |

| L                                     | <u>.</u>                          |                      | U                | U                |               |           | I                |                      | Ø           | 0                |                 |

| Transi                                | tion                              | table                | for              | D fl             | ip-flop:      | Trans     | ition            | table                | for         | Τf               | lip-flop :      |

| sym                                   | bol                               | QQ⁺                  | D                | _                |               | S         | ymbo             | ol QQ⁺               | Т           |                  |                 |

| 0                                     | )                                 | 00                   | 0                |                  |               |           | 0                | 00                   | 0           |                  |                 |

| 0                                     |                                   | 01                   | 1                |                  |               |           | α                | 01                   | 1           |                  |                 |

| β                                     | 5                                 | 10                   | 0                |                  |               |           | β                | 10                   | 1           |                  |                 |

| 1                                     |                                   | 11                   | 1                |                  |               |           | 1                | 11                   | 0           |                  |                 |

|                                       |                                   | hu / //              | (                |                  |               |           |                  |                      |             |                  |                 |

| http://akademi.it<br>http://www.buzlu |                                   |                      | ca/              |                  |               |           |                  | 2011                 | - 2023      | Fez              | a BUZLUCA 10.12 |

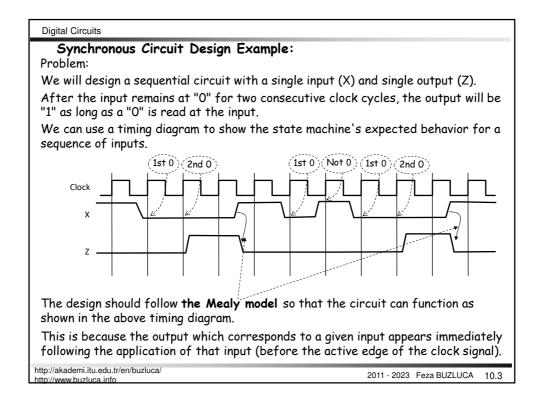

Digital Circuits

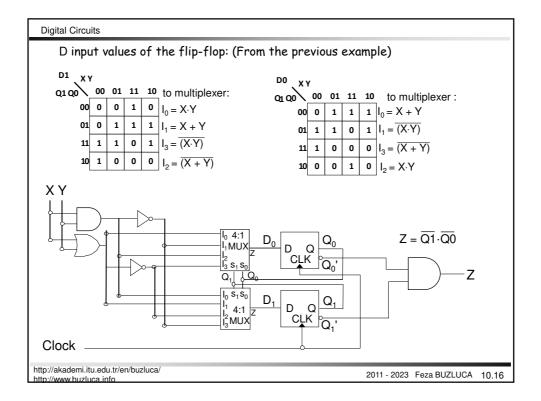

## Synchronous Circuit Design Example 2: Moore Model

Designing a circuit using the Moore model has the same design stages that we have already seen.

It is important to note that

- outputs depend ONLY on the states,

- because of this, each state corresponds to a single output.

## Problem:

We will design a synchronous sequential circuit with two inputs (X,Y) and a single output (Z).

If the number of 1s received at the input is a multiple of 4, the output of the circuit is 1. Otherwise, the output should be 0. If no 1s are received (the number of 1s is zero), the output should be 1.

## Solution:

The circuit should perform the modulo 4 operation, and if the result of theoperation is 0, the output should be 1. This FSM can be implemented with 4 states:1.Modulo 0: S02.Modulo 1: S13.Modulo 2: S23.Modulo 2: S23.Output = 03.Nodulo 2: S23.Output = 03.Modulo 2: S23.Modulo 2: S2</

| 4.                                       | Modulo 3: S3 | Output = 0 | number of incoming 1s mod 4 = 3 |       |

|------------------------------------------|--------------|------------|---------------------------------|-------|

| http://akademi.itu.<br>http://www.buzluc |              |            | 2011 - 2023 Feza BUZLUCA        | 10.13 |

| Digital Circu                                      | its                                                                                                                                                                                                   |                                                              |                            |                            |                                                              |                                                                                      |                                                  |                                                                                                                                                     |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------|----------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| State,<br>Mean<br>Modul<br>Modul<br>Modul<br>Modul | ing         S           0 0         S0           0 1         S1           0 2         S2                                                                                                              | 2:<br>Y <sub>00 01</sub><br>S0 S1<br>S1 S2<br>S2 S3<br>S3 S0 | 11<br>S2<br>S3<br>S0<br>S1 | 10<br>S1<br>S2<br>S3<br>S0 | <b>Z</b><br>1<br>0<br>0                                      | State coo<br>S0: 00<br>S1: 01<br>S2: 11<br>S3: 10<br>State var                       | -                                                |                                                                                                                                                     |

| Coded st                                           | ate/output 1           (Y           00         01         11           00         01         1           01         14         1           11         10         00           10         00         0 | <u>able:</u><br>10 <b>Z</b><br>1 01 1<br>2 11 0<br>10 0      |                            | Q0+)<br>D1<br>Q1 Q0        | x <sup>(·</sup> , y<br>X Y<br>00 0 0<br>01 0<br>11 1<br>10 1 | Q1, Q0<br>Q1'-X - Y<br>01 11 10<br>0 11 10<br>1 1 1<br>1 0 1<br>0 0 0<br>Q0 - X - Y' |                                                  | $\begin{array}{c} Q1' \cdot X \cdot Y' \\ p1 & 11 & 10 \\ \hline 1 & 1 & 1 \\ \hline 0 & 1 & 0 \\ \hline 0 & 0 & 0 \\ \hline 0 & 1 & 0 \end{array}$ |

| Since we a                                         | re using the                                                                                                                                                                                          | characte                                                     | risti                      |                            | ,                                                            |                                                                                      | $\frac{Q_0 \cdot x' \cdot y'}{Q^+ = D}, D_1 = C$ | $Q_{1^{+}}, D_{0}=Q_{0^{+}}$                                                                                                                        |

| C                                                  | 01= Q0·X'·Y +<br>00= Q1'·X'·Y                                                                                                                                                                         | + Q1'·X·Y                                                    |                            |                            |                                                              |                                                                                      | Z= Q1                                            | ' · Q0'                                                                                                                                             |

| http://akademi.it<br>http://www.buzlu              | u.edu.tr/en/buzluca<br>ca.info                                                                                                                                                                        |                                                              |                            |                            |                                                              |                                                                                      | 2011 - 2023 Feza                                 | BUZLUCA 10.14                                                                                                                                       |

| Digital Circuits                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

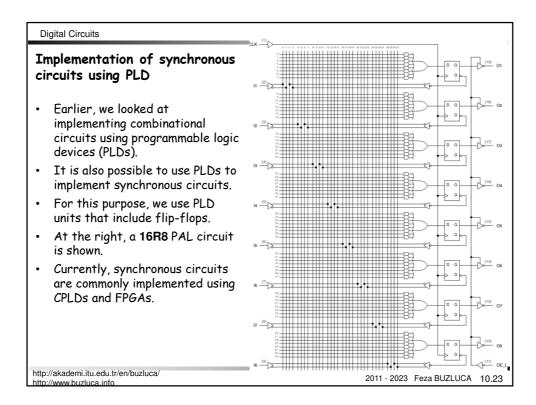

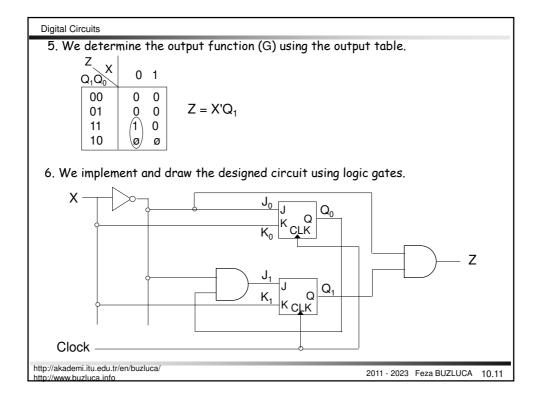

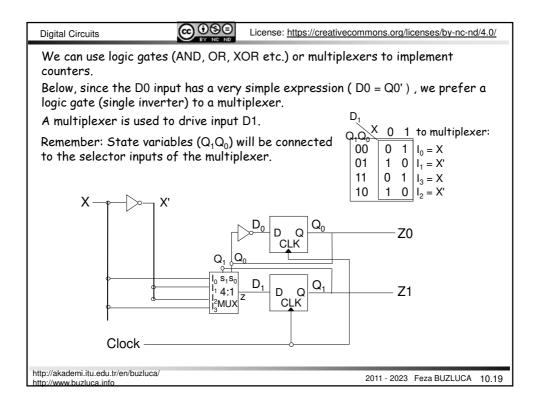

| Using Multiplexers for Synchronous Circuit Implementation                                                                                                                                                                          |

| If a synchronous sequential circuit is designed using D flip-flops, simpler implementations are possible if the inputs of the flip-flops are driven with multiplexers.                                                             |

| In this method,                                                                                                                                                                                                                    |

| <ul> <li>The input of each D flip-flop is driven by a separate multiplexer.</li> </ul>                                                                                                                                             |

| <ul> <li>The state variables (flip-flop outputs) are connected to the selector<br/>(control) inputs of the multiplexers. Therefore, each multiplexer selects one<br/>of its data inputs according to the current state.</li> </ul> |

| <ul> <li>The inputs of the multiplexer should have the necessary values that produce<br/>the next state of the machine.</li> </ul>                                                                                                 |

| <ul> <li>We obtain the values that will be applied to the inputs of the multiplexers<br/>from the rows of the state transition table.</li> </ul>                                                                                   |

| The same circuit designed in the previous example will be redesigned using multiplexers.                                                                                                                                           |

|                                                                                                                                                                                                                                    |

| nttp://akademi.itu.edu.tr/en/buzluca/ 2011 - 2023 Feza BUZLUCA 10.15                                                                                                                                                               |

| Digital Circuits                                                     |                                                                   |                                                                         |                               |

|----------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------|

| State diagra                                                         | m:                                                                | State table:                                                            |                               |

| X=                                                                   | 0                                                                 | Q <sub>1</sub> <sup>+</sup> Q <sub>0</sub> <sup>+</sup>                 |                               |

| X=0<br>X=0<br>X=1<br>X=1<br>X=1<br>X=1<br>X=1<br>X=1<br>X=1<br>X=1   | $X=1$ $X=0$ $1 \rightarrow 10^{-1}$ $X=0$ $X=0$ $X=0$ $X=0$ $X=0$ | Rows are ordered according code so that state table can a Karnaugh map. |                               |

| Designing the co                                                     | unter using D flip-                                               | -flops:                                                                 |                               |

| Recall:<br>$Q^+ = D$<br>Therefore,<br>$D_1 = Q_1^+$<br>$D_0 = Q_0^+$ | $\begin{array}{cccccccccccccccccccccccccccccccccccc$              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                   | Output:<br>Z0 = Q0<br>Z1 = Q1 |

|                                                                      | X'·(Q1⊕Q0) + X·(Q1<br>X⊕Q1⊕Q0                                     | ⊕Q0)' D0 = Q0'                                                          |                               |

| http://akademi.itu.edu.tr/en/b<br>http://www.buzluca.info            | uzluca/                                                           | 2011 - 2023                                                             | Feza BUZLUCA 10.18            |

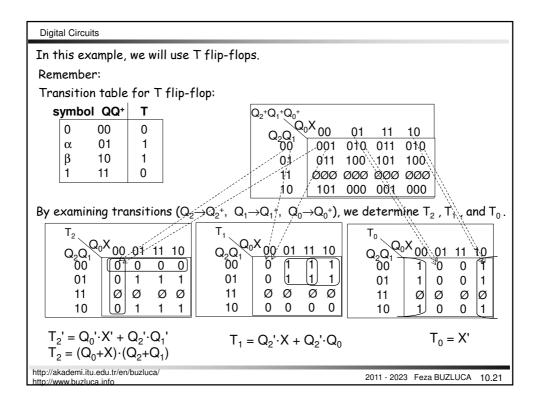

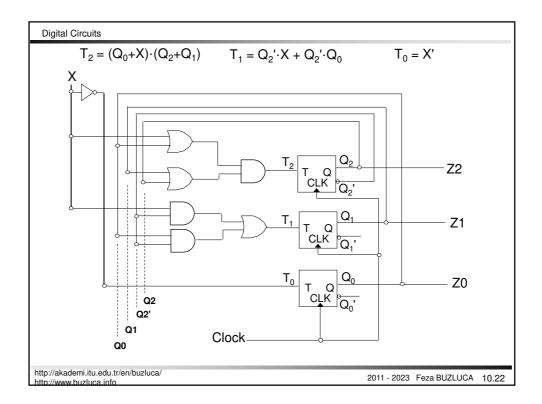

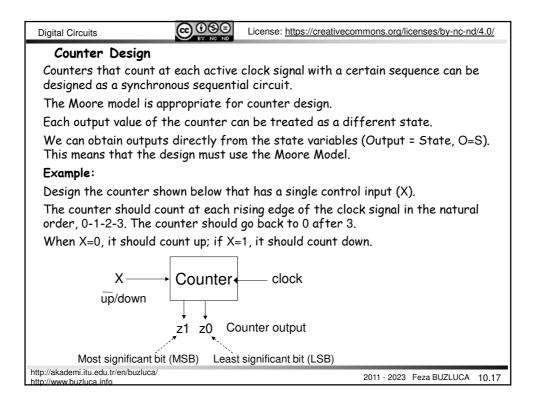

| Digital Circuits                      |                                                                         |

|---------------------------------------|-------------------------------------------------------------------------|

| control input (X).                    | e sequence 0-1-2-3-4-5 and has a single                                 |

| If X=0 count up by one; if X=1, coun  |                                                                         |

| (000) X=0 →(001)                      | <u>State table:</u><br>Q <sub>2</sub> +Q <sub>1</sub> +Q <sub>0</sub> + |

| X=0 X=1 X=1 X=0                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                   |

| We organize the state table           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                   |

| as a Karnaugh map:                    | 01 011 100 /101 100 <sup>+</sup><br>11 ØØØ ØØØ ØØØ                      |

| http://akademi.itu.edu.tr/en/buzluca/ | 10 101 000 001 000                                                      |

| http://www.buzluca.info               | 2011 - 2023 Feza BUZLUCA 10.20                                          |