| Digital Circuits License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design of Clocked Synchronous Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Steps of sequential circuit design (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

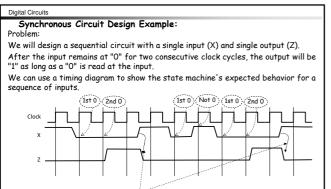

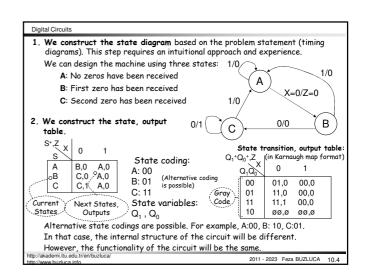

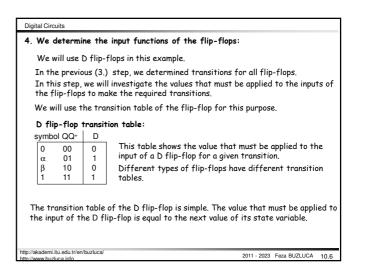

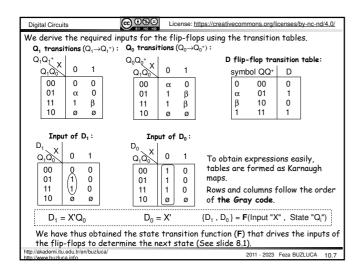

| The design of a sequential circuit starts with the problem statement which specifies the desired relationship between the input and output sequences (scenario). The process of designing a circuit to perform a given logical function is quite similar to the process of designing a computer program to perform a given task. Sirist, we should describe and appropriately model the real-world problem. Then, we should design a circuit to solve the problem. Sesigning a sequential circuit consists of the following steps: We describe the problem (functional requirements of the circuit) verbally. We can use timing diagrams to avoid uncertainties. We determine the states that will make up the finite state machine (FSM). a) We determine the state transitions due on the inputs and current states. b) We construct the state transition and output tables. We can use a state diagram if it makes the design easier. C) We reduce the number of states in the state table (if applicable). The purpose is to build a correctly functioning machine with the fewest possible number of states. | <ol> <li>Assigning codes to each state: A binary code is assigned to each state. If there are n states, the number of variables (number of flip-flops) m is computed as follows:<br/>m= [log<sub>2</sub>n]<br/>where [x] denotes the ceiling function. For example, [4.1] = 5 and [4.0] = 4</li> <li>We construct the state transition and output table based on the values of the state variables.</li> <li>We decide what type of flip-flops we will use.</li> <li>Using the transition table for the selected flip-flop type, we determine the inputs of the flip-flops. We obtain the function (F) that drives the flip-flops.</li> <li>From the output table, we obtain the output function (G).</li> <li>We design combinational circuits for the functions (F and G) and impleme each with the minimum cost.</li> </ol> |

http://akademi.itu.edu.tr/en/buzluca/

d) This process is similar to the process of designing a computer program; that is why

2011 - 2023 Feza BUZLUCA

it requires an intuitional approach.

akademi.itu.edu.tr/en/buzluca/

The design should follow **the Mealy model** so that the circuit can function as shown in the above timing diagram.

This is because the output which corresponds to a given input appears immediately following the application of that input (before the active edge of the clock signal). http://www.huture.info

2011 - 2023 Feza BUZLUCA 10.2

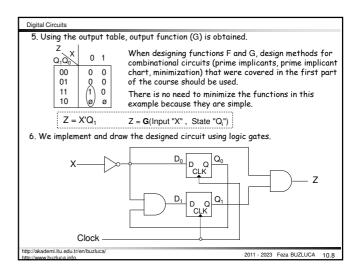

| 5. We determine the transitions of            |                  | Q1+                                                            | Q <sub>0</sub> <sup>+</sup> ,Z | Sta<br>0                      | ate ti<br>1 | ransition | table                                        | 2    |                    |

|-----------------------------------------------|------------------|----------------------------------------------------------------|--------------------------------|-------------------------------|-------------|-----------|----------------------------------------------|------|--------------------|

| state variables:                              | state variables: |                                                                |                                |                               |             |           |                                              |      |                    |

| Using the state transition table of the       |                  |                                                                |                                | 00                            | 01          | 00        |                                              |      |                    |

| circuit, we determine the transitions of      |                  |                                                                |                                | 01                            | <u></u> 11  | N 00      |                                              |      |                    |

| each state variable (flip-flop) separately.   |                  |                                                                |                                | 11                            | 11          | 00        |                                              |      |                    |

| For this solution, we need two flip-flops,    |                  |                                                                |                                | 10                            | øø          | ØØ        | N                                            |      |                    |

| i.e., Q1 and Q2.                              |                  | • • •                                                          |                                |                               |             |           | Q                                            | tran | sition             |

|                                               |                  |                                                                | 0                              | 1Q1+                          |             |           | $Q_0 Q_0^+$                                  | (Q₀: | →Q <sub>0</sub> +) |

|                                               | (                | Q <sub>1</sub> transitio<br>(Q <sub>1</sub> →Q <sub>1</sub> +) | ns:                            | Q <sub>1</sub> Q <sub>0</sub> | O           | 1         | Q1Q0                                         | 0    | 1                  |

|                                               |                  |                                                                |                                | 00                            | ŐŐ          | 00        | 00                                           | 01   | 00                 |

|                                               | symbol           | QQ+                                                            |                                | 01                            | 01          | 00        | 01                                           | 11   | 10                 |

| we assign symbolic                            | 0                | 00                                                             |                                | 11                            | 11          | 10        | 11                                           | 11   | 10                 |

| names to transitions                          | α                | 01                                                             |                                | 10                            | ø           | ø         | 10                                           | ø    | ø                  |

| and reorganize the                            | β                | 10                                                             | ~                              |                               | 1           |           |                                              |      |                    |

| tables with these                             | 1                | 11                                                             | G                              | 0₁Q1 <sup>+</sup> X           | 0           | 1         | Q <sub>0</sub> Q <sub>0</sub> <sup>+</sup> X |      |                    |

| symbols.                                      |                  |                                                                |                                | Q <sub>1</sub> Q <sub>0</sub> | 0           |           |                                              | 0    | 1                  |

| <b>T</b> I I I                                |                  |                                                                |                                | 00                            | 0           | 0         | 00                                           | α    | 0                  |

| Thus, we have determined what transition      |                  |                                                                |                                | 01                            | α           | 0         | 01                                           | 1    | β                  |

| each state variable (flip-flop) will make for |                  |                                                                | r                              | 11                            | 1           | β         | 11                                           | 1    | β                  |

| each input value and state.                   |                  |                                                                |                                | 10                            | ø           | ø         | 10                                           | ø    | ø                  |

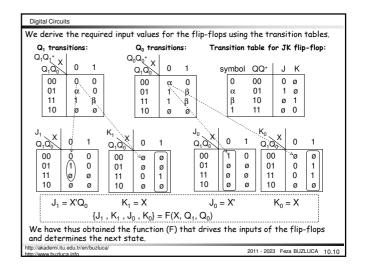

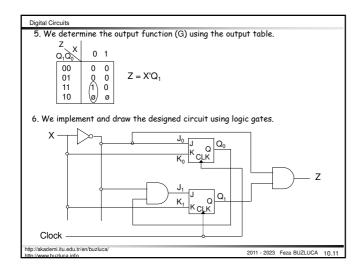

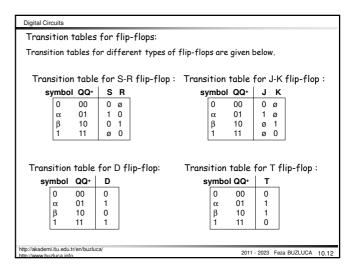

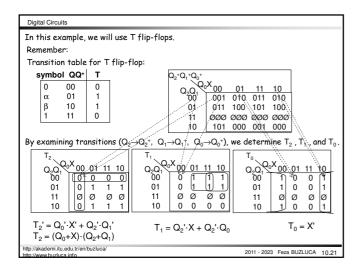

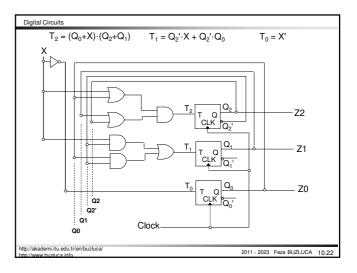

| Digital Circuits                                       |                                                                                                           |              |                                                                               |                               |                                                             |    |  |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------|----|--|

| Example: Same circuit designed using J-K flip-flops    |                                                                                                           |              |                                                                               |                               |                                                             |    |  |

| The first t                                            | The first three steps are the same.                                                                       |              |                                                                               |                               |                                                             |    |  |

| 4. In this                                             | <ol> <li>In this example, we will use positive edge-triggered J-K flip-flops.</li> </ol>                  |              |                                                                               |                               |                                                             |    |  |

| J-K flip-flo                                           | J-K flip-flop transition table:                                                                           |              |                                                                               |                               |                                                             |    |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |                                                                                                           |              |                                                                               |                               |                                                             |    |  |

| Q1+Q0+,Z                                               | •                                                                                                         |              | Q <sub>1</sub> transition                                                     | <b>is (</b> Q <sub>1</sub> →C |                                                             | ): |  |

|                                                        | 0                                                                                                         | 1            | Q <sub>1</sub> Q <sub>1</sub> <sup>+</sup> X<br>Q <sub>1</sub> Q <sub>0</sub> | 0 1                           | $\begin{array}{c c} Q_0 Q_0^{+} \\ Q_1 Q_0 \end{array} 0 1$ |    |  |

| 00                                                     | 01,0                                                                                                      | 00,0         | 00                                                                            | 0 0                           | 00 α 0                                                      |    |  |

| 01                                                     | 11,0<br>11.1                                                                                              | 00,0<br>00.0 | 01                                                                            | α 0<br>1 β                    | 01 1 β<br>11 1 β                                            |    |  |

| 10                                                     | øø,ø                                                                                                      | ØØ,Ø         | 10                                                                            | øø                            | 10 ø ø                                                      |    |  |

|                                                        | http://akademi.itu.edu.tr/en/buzluca/<br>http://akademi.itu.edu.tr/en/buzluca/<br>http://www.huzluca.info |              |                                                                               |                               |                                                             | .9 |  |

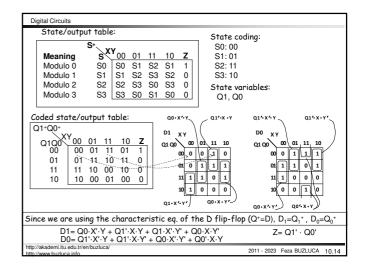

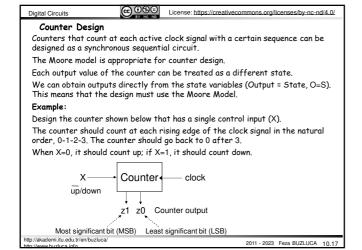

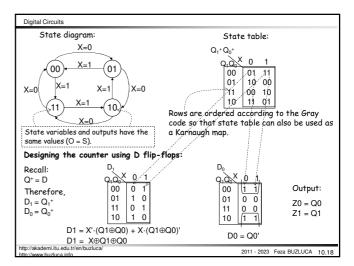

| Synchronous | Circuit | Design | Example | 2: | Moore Model |

|-------------|---------|--------|---------|----|-------------|

Designing a circuit using the Moore model has the same design stages that we have already seen.

It is important to note that

$\cdot$  outputs depend ONLY on the states,

• because of this, each state corresponds to a single output.

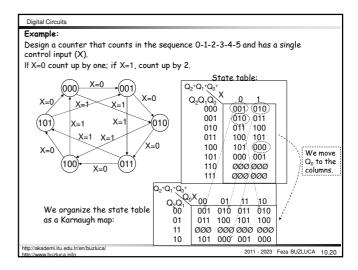

## Problem

Digital Circuits

We will design a synchronous sequential circuit with two inputs (X,Y) and a single output (Z).

If the number of 1s received at the input is a multiple of 4, the output of the circuit is 1. Otherwise, the output should be 0. If no 1s are received (the number of 1s is zero), the output should be 1.

## Solution

The circuit should perform the modulo 4 operation, and if the result of the

| operatio           | n is 0, the outpu   | t snould de 1. | This FSM can be implemented with 4 states: |

|--------------------|---------------------|----------------|--------------------------------------------|

| 1.                 | Modulo 0: S0        | Output = 1     | number of incoming 1s mod 4 = 0            |

| 2.                 | Modulo 1: S1        | Output = 0     | number of incoming 1s mod 4 = 1            |

| 3.                 | Modulo 2: S2        | Output = 0     | number of incoming 1s mod 4 = 2            |

| 4.                 |                     | Output = 0     | number of incoming 1s mod 4 = 3            |

| http://akademi.itu | .edu.tr/en/buzluca/ |                | 2011 2022 Ferre BUZUUCA 40.40              |

## Digital Circuits

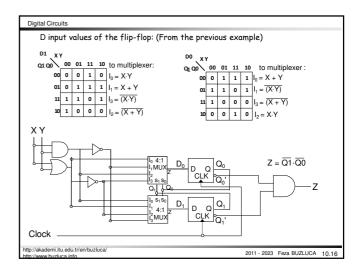

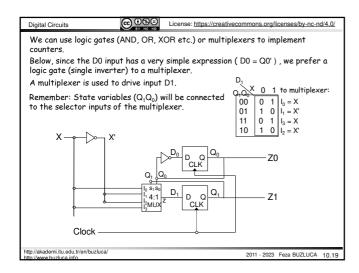

## Using Multiplexers for Synchronous Circuit Implementation

If a synchronous sequential circuit is designed using D flip-flops, simpler implementations are possible if the inputs of the flip-flops are driven with multiplexers.

In this method,

- The input of each D flip-flop is driven by a separate multiplexer.

- The state variables (flip-flop outputs) are connected to the selector (control) inputs of the multiplexers. Therefore, each multiplexer selects one of its data inputs according to the current state.

- The inputs of the multiplexer should have the necessary values that produce the next state of the machine.

- We obtain the values that will be applied to the inputs of the multiplexers from the rows of the state transition table.

- The same circuit designed in the previous example will be redesigned using multiplexers.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA 10.15

| Digital Circuits                                                                                                                   |                              |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Implementation of synchronous circuits using PLD                                                                                   |                              |

| <ul> <li>Earlier, we looked at<br/>implementing combinational<br/>circuits using programmable logic<br/>devices (PLDs).</li> </ul> |                              |

| <ul> <li>It is also possible to use PLDs to<br/>implement synchronous circuits.</li> </ul>                                         |                              |

| <ul> <li>For this purpose, we use PLD<br/>units that include flip-flops.</li> </ul>                                                |                              |

| • At the right, a <b>16R8</b> PAL circuit is shown.                                                                                |                              |

| • Currently, synchronous circuits are commonly implemented using CPLDs and FPGAs.                                                  |                              |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                              | 2011-2023 Feza BUZLUCA 10.23 |