| Digital Circuits License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design of Clocked Synchronous Sequential Circuits                                                                                                                        |

| The design of a sequential circuit starts with the problem statement which specifies the desired relationship between the input and output sequences (scenario).         |

| The process of designing a circuit to perform a given logical function is quite similar to the process of designing a computer program to perform a given task.          |

| First, we should describe and appropriately model the real-world problem.                                                                                                |

| Then, we should design a circuit to solve the problem.                                                                                                                   |

| Designing a sequential circuit consists of the following steps:                                                                                                          |

| 1. We describe the problem ( <b>functional requirements</b> of the circuit) verbally. We can use timing diagrams to avoid uncertainties.                                 |

| 2. We decide which design model (Mealy/Moore) would better represent the circuit.                                                                                        |

| 3. We determine the <b>states</b> that will make up the finite state machine (FSM).                                                                                      |

| a) We determine the state transitions based on the inputs and current states.                                                                                            |

| b) We construct the state transition and output tables. We can use a state diagram if it makes the design easier.                                                        |

| c) We reduce the number of states in the state table (if applicable). The purpose is to build a correctly functioning machine with the fewest possible number of states. |

| <ul> <li>d) This process is similar to the process of designing a computer program; that is why<br/>it requires an intuitional approach.</li> </ul>                      |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011 - 2023 Feza BUZLUCA 10.1                                                                           |

| Digital Circuits                                                                                                                                      |                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Steps of sequential circuit design (cont'd)                                                                                                           |                               |

| <ol> <li>Assigning codes to each state: A binary code is a<br/>there are n states, the number of variables (numbe<br/>computed as follows:</li> </ol> |                               |

| $m = \lceil \log_2 n \rceil$                                                                                                                          |                               |

| where $\lceil x \rceil$ denotes the ceiling function. For example,                                                                                    | [4.1] = 5 and $[4.0] = 4$ .   |

| <ol> <li>We construct the state transition and output table<br/>the state variables.</li> </ol>                                                       | e based on the values of      |

| 6. We decide what type of flip-flops we will use.                                                                                                     |                               |

| <ol> <li>Using the transition table for the selected flip-flo<br/>inputs of the flip-flops. We obtain the function (F<br/>flops.</li> </ol>           |                               |

| 8. From the output table, we obtain the output funct                                                                                                  | ion (G).                      |

| <ol> <li>We design combinational circuits for the function<br/>each with the minimum cost.</li> </ol>                                                 | ns (F and G) and implement    |

|                                                                                                                                                       |                               |

|                                                                                                                                                       |                               |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                 | 2011 - 2023 Feza BUZLUCA 10.2 |

| http://www.buzluca.info                                                                                                                               | 10.2                          |

### Digital Circuits

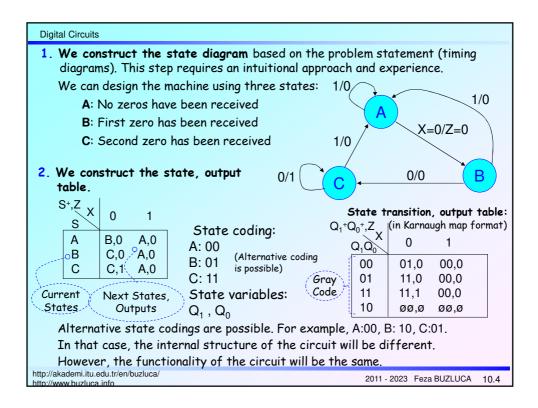

## Synchronous Circuit Design Example:

## Problem:

We will design a sequential circuit with a single input (X) and single output (Z). After the input remains at "O" for two consecutive clock cycles, the output will be "1" as long as a "O" is read at the input.

We can use a timing diagram to show the state machine's expected behavior for a sequence of inputs.

The design should follow **the Mealy model** so that the circuit can function as shown in the above timing diagram.

This is because the output which corresponds to a given input appears immediately following the application of that input (before the active edge of the clock signal).

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA 10.3

| <ul> <li>Digital Circuits</li> <li>3. We determine the transitions of state variables:</li> <li>Using the state transition table of the circuit, we determine the transitions of each state variable (flip-flop) separately.</li> <li>For this solution, we need two flip-flops,</li> </ul> | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| i.e., $Q_1$ and $Q_2$ .<br>$Q_1$ transition<br>$(Q_1 \rightarrow Q_1^+)$                                                                                                                                                                                                                    | $Q_1 Q_0$ $Q_1$ $Q_1 Q_0$ $Q_1$                                                                                                                                                                                                                                                                                                  |

| To simplify notation,<br>we assign symbolicsymbol<br>0QQ+names to transitions<br>and reorganize the000β10                                                                                                                                                                                   | 00         00         00         00         01         01         00           01         01         00         01         11         10         11         10           11         11         10         11         11         10         Ø         Ø           10         Ø         Ø         10         Ø         Ø         Ø |

| and reorganize the $\beta$ 10<br>tables with these 1 11<br>symbols.                                                                                                                                                                                                                         | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                            |

| Thus, we have determined what transition<br>each state variable (flip-flop) will make for<br>each input value and state.                                                                                                                                                                    | $01 \alpha 0 01 1 \beta$                                                                                                                                                                                                                                                                                                         |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                                                                                                                                                                            | 2011 - 2023 Feza BUZLUCA 10.5                                                                                                                                                                                                                                                                                                    |

| Digital Circuits                                                                                                                                                    |                                                                                                                                                                                                                    |                                                                                                       |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

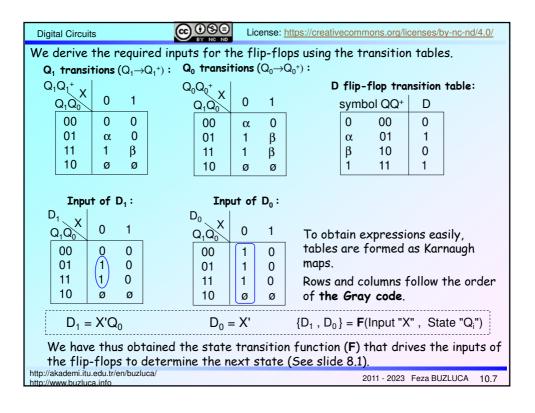

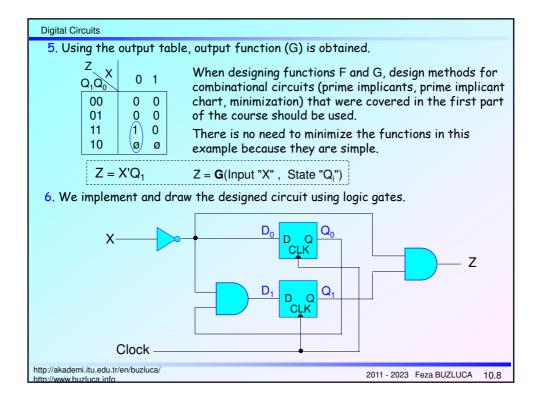

| 4. We determi                                                                                                                                                       | ne the                                                                                                                                                                                                             | input functions of the flip-flops:                                                                    |  |  |  |  |

| We will use l                                                                                                                                                       | ) flip-                                                                                                                                                                                                            | flops in this example.                                                                                |  |  |  |  |

| In this step,                                                                                                                                                       | In the previous (3.) step, we determined transitions for all flip-flops.<br>In this step, we will investigate the values that must be applied to the inputs of<br>the flip-flops to make the required transitions. |                                                                                                       |  |  |  |  |

| We will use t                                                                                                                                                       | he tra                                                                                                                                                                                                             | nsition table of the flip-flop for this purpose.                                                      |  |  |  |  |

| D flip-flop 1                                                                                                                                                       | ransit                                                                                                                                                                                                             | tion table:                                                                                           |  |  |  |  |

| symbol QQ <sup>+</sup>                                                                                                                                              | D                                                                                                                                                                                                                  |                                                                                                       |  |  |  |  |

| $\begin{bmatrix} 0 & 00 \\ \alpha & 01 \end{bmatrix}$                                                                                                               | 0                                                                                                                                                                                                                  | This table shows the value that must be applied to the input of a D flip-flop for a given transition. |  |  |  |  |

| β 10<br>1 11                                                                                                                                                        | 0<br>1                                                                                                                                                                                                             | Different types of flip-flops have different transition tables.                                       |  |  |  |  |

| The transition table of the D flip-flop is simple. The value that must be applied to the input of the D flip-flop is equal to the next value of its state variable. |                                                                                                                                                                                                                    |                                                                                                       |  |  |  |  |

| http://akademi.itu.edu.tr/en<br>http://www.buzluca.info                                                                                                             | /buzluca/                                                                                                                                                                                                          | 2011 - 2023 Feza BUZLUCA 10.6                                                                         |  |  |  |  |

Digital Circuits

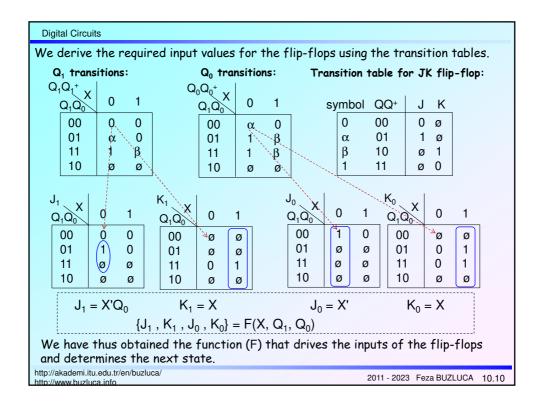

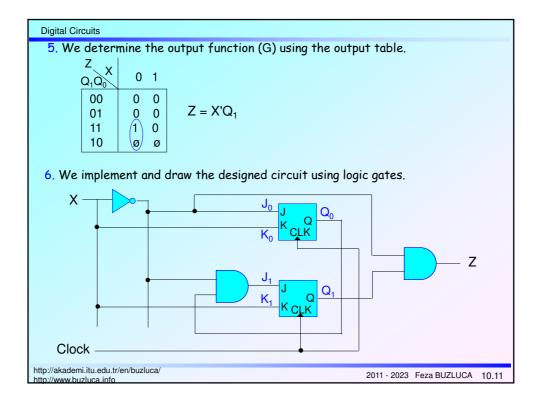

Example: Same circuit designed using J-K flip-flops

The first three steps are the same.

4. In this example, we will use positive edge-triggered J-K flip-flops.

J-K flip-flop transition table:

| S | ymbol | QQ+ | J | Κ |   |

|---|-------|-----|---|---|---|

|   | 0     | 00  | 0 | ø |   |

|   | α     | 01  | 1 | ø |   |

|   | β     | 10  | ø | 1 | 1 |

|   | 1     | 11  | ø | 0 |   |

|   |       |     |   |   |   |

Using J-K flip-flops instead of D flip-flops generally yields simpler logic functions for the next state. However, since the functions in this example are already simple, the J-K flip-flop yields no further simplification.

We had determined the transitions of state variables from the state transition table in step 3.  $\Omega_{1}$  transitions  $(\Omega_{1} \rightarrow \Omega_{1}^{+})$ ;  $\Omega_{2}$  transitions  $(\Omega_{2} \rightarrow \Omega_{2}^{+})$ ;

|                |                      | $\mathbf{u}_1$ munshing                               | <b>ms</b> (C                                                              | $\mathbf{x}_1 \rightarrow \mathbf{u}_1$                                                                                    | $\sim$ $\alpha_0$ mans                                                                                                                                                                                                                                                                                                    | 1110115                                               | $(\mathbf{Q}_0 \rightarrow \mathbf{Q})$               | $\mathbf{Q}_0$                                        |

|----------------|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|

|                |                      | $Q_1 Q_1^+$                                           |                                                                           |                                                                                                                            | $Q_0 Q_0^+$                                                                                                                                                                                                                                                                                                               |                                                       |                                                       |                                                       |

| 0              | 1                    | $Q_1 Q_0$                                             | 0                                                                         | 1                                                                                                                          | $Q_1 Q_0$                                                                                                                                                                                                                                                                                                                 | 0                                                     | 1                                                     |                                                       |

| 01,0           | 00,0                 | 00                                                    | 0                                                                         | 0                                                                                                                          | 00                                                                                                                                                                                                                                                                                                                        | α                                                     | 0                                                     |                                                       |

| 11,0           | 00,0                 | 01                                                    | α                                                                         | 0                                                                                                                          | 01                                                                                                                                                                                                                                                                                                                        | 1                                                     | β                                                     |                                                       |

| 11,1           | 00,0                 | 11                                                    | 1                                                                         | β                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                        | 1                                                     | β                                                     |                                                       |

| øø,ø           | øø,ø                 | 10                                                    | ø                                                                         | ø                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                        | ø                                                     | ø                                                     |                                                       |

| .tr/en/buzluca | a/                   |                                                       |                                                                           |                                                                                                                            | 2011 - 2023 F                                                                                                                                                                                                                                                                                                             | eza BUZ                                               | LUCA                                                  | 10.9                                                  |

|                | 11,0<br>11,1<br>ØØ,Ø | 11,0 00,0<br>11,1 00,0<br>ØØ,Ø ØØ,Ø<br>tr/en/buzluca/ | 0 1<br>01,0 00,0<br>11,0 00,0<br>11,1 00,0<br>ØØ,Ø ØØ,Ø<br>tr/en/buzluca/ | 0     1       01,0     00,0       11,0     00,0       11,1     00,0       11,1     00,0       11     1       0ø,ø     øø,ø | $\begin{array}{c c} 0 & 1 \\ \hline 01,0 & 00,0 \\ 11,0 & 00,0 \\ 11,1 & 00,0 \\ \emptyset \emptyset, \emptyset & \emptyset \emptyset, \emptyset \end{array} \qquad \begin{array}{c} Q_1 Q_1^+ X \\ Q_1 Q_0 \\ 0 & 1 \\ \hline 00 & 0 & 0 \\ 01 & \alpha & 0 \\ 11 & 1 & \beta \\ 10 & \emptyset & \emptyset \end{array}$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

| Digital Ci    | rcuits                                                               |                      |                          |                |       |                  |                      |                  |                  |                 |

|---------------|----------------------------------------------------------------------|----------------------|--------------------------|----------------|-------|------------------|----------------------|------------------|------------------|-----------------|

| Trans         | ition                                                                | tables               | for f                    | ip-flops:      |       |                  |                      |                  |                  |                 |

| Transi        | Transition tables for different types of flip-flops are given below. |                      |                          |                |       |                  |                      |                  |                  |                 |

| Trar          | nsition                                                              | n table              | for S                    | -R flip-flop : | Trans | ition            | table <sup>.</sup>   | for              | J-K              | flip-flop :     |

| s             | ymbo                                                                 | I QQ⁺                | SF                       | 2              | sy    | mbo              | QQ⁺                  | J                | Κ                | _               |

|               | 0<br>α<br>β<br>1                                                     | 00<br>01<br>10<br>11 | 0 ø<br>1 0<br>0 1<br>ø 0 |                |       | 0<br>α<br>β<br>1 | 00<br>01<br>10<br>11 | 0<br>1<br>Ø      | ø<br>ø<br>1<br>0 |                 |

| Trans         | sition                                                               | table                | for D                    | flip-flop:     | Trans | ition            | table                | for              | Тf               | lip-flop:       |

| sy            | mbol                                                                 | QQ⁺                  | D                        |                | s     | ymbo             | ol QQ⁺               | Т                |                  |                 |

|               | 0<br>α<br>β<br>1                                                     | 00<br>01<br>10<br>11 | 0<br>1<br>0<br>1         |                |       | 0<br>α<br>β<br>1 | 00<br>01<br>10<br>11 | 0<br>1<br>1<br>0 |                  |                 |

| http://akaden |                                                                      |                      | ca/                      |                |       |                  | 2011                 | - 2023           | Fez              | a BUZLUCA 10.12 |

#### **Digital Circuits**

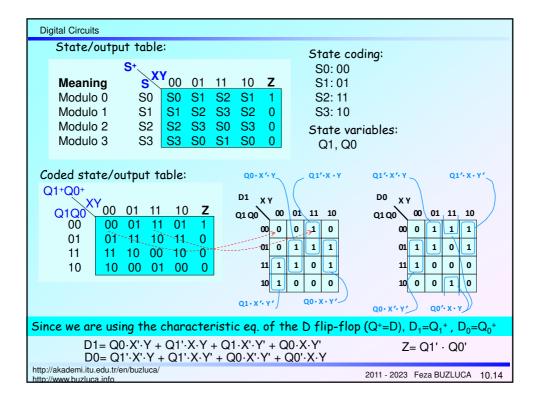

# Synchronous Circuit Design Example 2: Moore Model

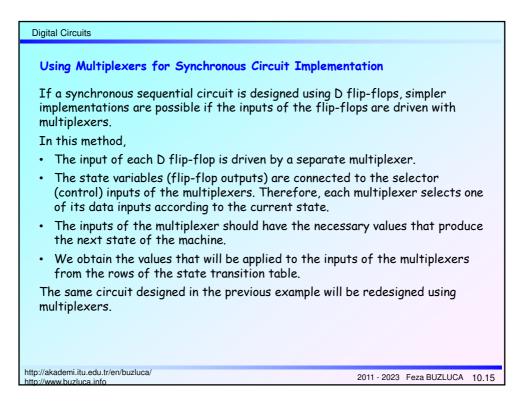

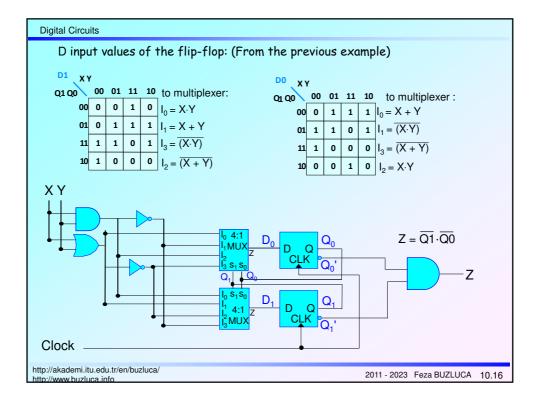

Designing a circuit using the Moore model has the same design stages that we have already seen.

It is important to note that

- outputs depend ONLY on the states,

- · because of this, each state corresponds to a single output.

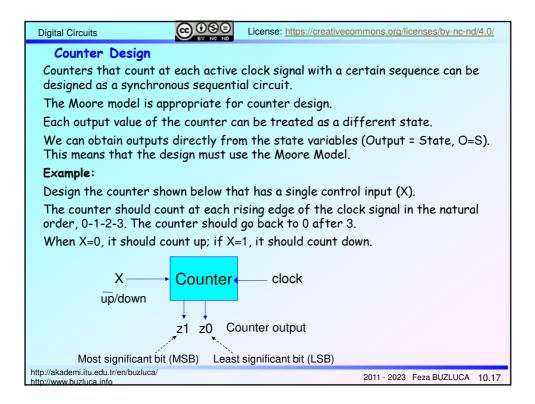

## Problem:

We will design a synchronous sequential circuit with two inputs (X,Y) and a single output (Z).

If the number of 1s received at the input is a multiple of 4, the output of the circuit is 1. Otherwise, the output should be 0. If no 1s are received (the number of 1s is zero), the output should be 1.

### Solution:

The circuit should perform the modulo 4 operation, and if the result of the operation is 0, the output should be 1. This FSM can be implemented with 4 states: Modulo 0: S0 Output = 1 number of incoming 1s mod 4 = 01. Modulo 1: S1 Output = 0number of incoming  $1 \le \mod 4 = 1$ 2. 3. Modulo 2: S2 Output = 0number of incoming 1s mod 4 = 24. Modulo 3: S3 Output = 0 number of incoming  $1 \le \mod 4 = 3$ http://akademi.itu.edu.tr/en/buzluca/ 2011 - 2023 Feza BUZLUCA 10.13 ttp://www.buzluca.info

| Digital Circuits                                                          |                                                                                      |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| State diagram:                                                            | State table:                                                                         |

| X=0                                                                       | Q <sub>1</sub> <sup>+</sup> Q <sub>0</sub> <sup>+</sup>                              |

| x 00 ← X=1 01                                                             | $Q_1 Q_0 \times 0 1$                                                                 |

|                                                                           | 00 01 11<br>01 10 00                                                                 |

| X=0 X=1 X=1 X=0                                                           | 71 00 10                                                                             |

| X=1 10                                                                    | 10 11 01                                                                             |

| X=0                                                                       | Row's are ordered according to the Gray code so that state table can also be used as |

| State variables and outputs have the                                      | a Karnaugh map.                                                                      |

| same values (O = S).                                                      |                                                                                      |

| Designing the counter using D flip                                        | -flops:                                                                              |

| Recall:                                                                   |                                                                                      |

| $Q^+ = D$ $Q_1 Q_0 0 1$                                                   | 00 1 1 Output:                                                                       |

| Therefore, $00$ $01$ $1$ $0$ $D_1 = Q_1^+$ $01$ $1$ $0$ $0$ $0$ $1$ $0$   | $\begin{array}{c} 00 \\ 01 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0$                  |

| $D_0 = Q_0^+$ 11 0 1                                                      | 11 0 0 71 = 01                                                                       |

|                                                                           |                                                                                      |

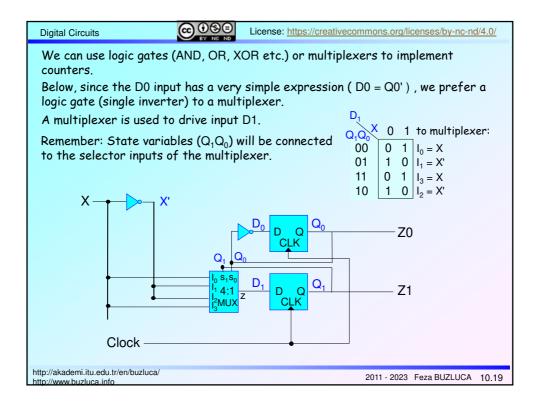

| $D1 = X' \cdot (Q1 \oplus Q0) + X \cdot (Q)$ $D1 = X \oplus Q1 \oplus Q0$ | D0 = Q0'                                                                             |

| http://akademi.itu.edu.tr/en/buzluca/                                     | 2011 - 2023 Feza BUZLUCA 10.18                                                       |

| Digital Circuits                                                                                               |                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

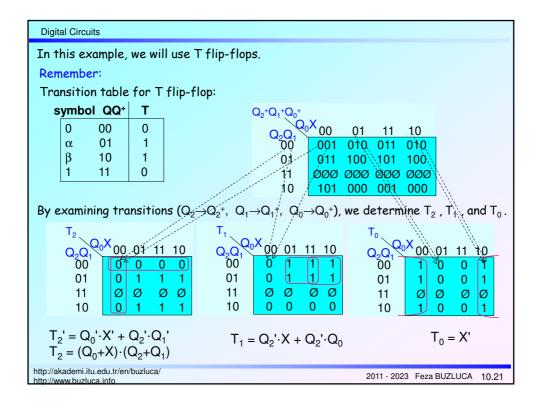

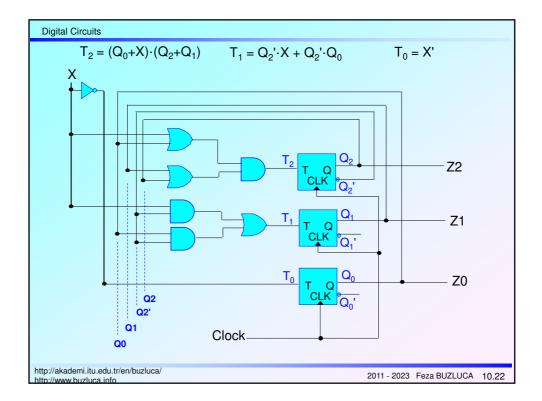

| Example:<br>Design a counter that counts in the<br>control input (X).<br>If X=0 count up by one; if X=1, count | e sequence 0-1-2-3-4-5 and has a single                                                                                                                                   |

| $\frac{1}{000} \times = 0 \longrightarrow 001$                                                                 | State table:<br>$Q_2^+Q_1^+Q_0^+$                                                                                                                                         |

| X=0 X=1 X=1 X=0                                                                                                | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                     |

| We organize the state table<br>as a Karnaugh map:                                                              | $\begin{array}{c} Q_2 + Q_1 + Q_0 + \\ Q_2 Q_1 & Q_0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 1 \\ 1 \\ 0 \\ 1 \\ 0 \\ 1 \\ 0 \\ 1 \\ 0 \\ 1 \\ 0 \\ 1 \\ 0 \\ 1 \\ 0 \\ 0$ |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                               | 2011 - 2023 Feza BUZLUCA 10.20                                                                                                                                            |