| Digital Circuits   | License: <u>https://creativecommons.org/licenses/by-nc-nd/4.0/</u>                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Combi              | inational Circuits As Building Blocks                                                                                       |

|                    | circuits can perform commonly used operations (such as ons, comparison, selection, decoding, etc.)                          |

|                    | ponding logic structures (such as adders, multiplexers, and orming these operations.                                        |

|                    | ng every complex function with basic logic gates, using these<br>makes the design simpler.                                  |

|                    | tionality often matches a designer's level of thinking when<br>problem into smaller chunks (like functions in programming). |

| These structures c | an be interconnected to construct more extensive systems.                                                                   |

| We design hardwar  | e using a hierarchical approach:                                                                                            |

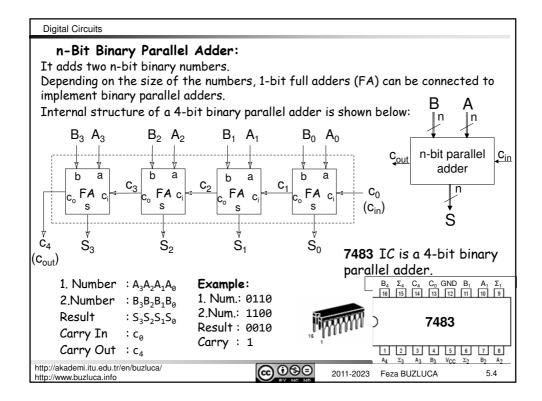

| • We design a sma  | ll component (e.g., a 1-bit adder) using basic logic gates.                                                                 |

|                    | component by interconnecting many copies of the small<br>ew extra gates (e.g., a 32-bit adder).                             |

| • We build chips b | y interconnecting many large components (e.g., a CPU).                                                                      |

|                    | is truly made out of many gates but using a hierarchy makes<br>ass faster and easier.                                       |

| Digital Circuits                                                                                                        |                                                                          |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Half Adder:<br>It adds two 1-bit numbers (without carry input).<br>Remember the rules of binary addition on slide 1.22. | Truth table:<br><u>a b c s</u><br>0 0 0 0<br>0 1 0 1<br>1 0 0 1<br>1 1 0 |

| From the truth table, the logical $a$<br>expression is obtained.<br>$s = a\overline{b} + \overline{a}b$<br>c = ab       | s<br>c                                                                   |

| The circuit can also be implemented using $a_{\perp}$<br>XOR gates. $b_{\perp}$<br>$s = a \oplus b$<br>c = ab           | s<br>c                                                                   |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                   | -2023 Feza BUZLUCA 5.2                                                   |

| Digital Circuits                                                                                                                                                                        |                                                                                                    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|

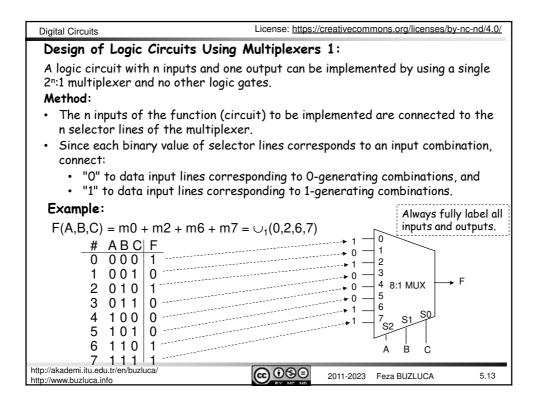

| <b>Design of Logic Circuits Using Multiplexers 2:</b><br>A logic circuit with n inputs and one output can be implemented using a single 2 <sup>n-1</sup> :1 multiplexer and a NOT gate. |                                                                                                    |  |  |  |

| <ul> <li>Method:</li> <li>Connect the n-1 inputs (variables)<br/>multiplexer.</li> <li>Then, connect the remaining single</li> </ul>                                                    | of the function to the n-1 select lines of the<br>e variable, or its complement, or 0, or 1 to the |  |  |  |

| Example:<br>F(A,B,C) = m0 + m2 + m6 + m7 = 0<br>Reminder: $1 - 1$<br>Solution with $1 - 2$<br>a 8:1 MUX: 0 - 3<br>(Previous method) $0 - 4 8:1 MUX \rightarrow F$                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                              |  |  |  |

| 0 - 5<br>1 - 6<br>7 - 5<br>7 - 5<br>7 - 5<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7<br>- 7                                                                                       | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                              |  |  |  |

| Digital Circuits                                                                                                                         |                                   |                                                                      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------------------------------------------|--|--|

| Demultiplexer:                                                                                                                           |                                   |                                                                      |  |  |

| • 1 data input, n selector (control) lines, 2 <sup>n</sup> data outputs. $I \longrightarrow 1:2^n \xrightarrow{2^n}_{\longrightarrow} 7$ |                                   |                                                                      |  |  |

| • It selects one of the many data output lines and connects it to the single input.                                                      |                                   |                                                                      |  |  |

| • The binary value on the select inputs determines the output S<br>line to which the data input is forwarded.                            |                                   |                                                                      |  |  |

| •The value on the not-sel                                                                                                                | ected output lines is '           | '0".                                                                 |  |  |

| • Demultiplexers are nam                                                                                                                 | ed <b>1:m</b> , based on the      | number of data outputs.                                              |  |  |

| Example: 1:2 Demultiple>                                                                                                                 | er<br>Function Table:             | Truth Table:                                                         |  |  |

| $G \longrightarrow 1:2 \longrightarrow 00$<br>DeMUX \longrightarrow 01                                                                   | s   O <sub>1</sub> O <sub>0</sub> | $\frac{\mathbf{s}  \mathbf{G}  \mathbf{O}_1  \mathbf{O}_0}{0 0 0 0}$ |  |  |

| s                                                                                                                                        | 0 0 G<br>1 G 0                    | 0 1 0 1<br>1 0 0 0                                                   |  |  |

| G 00                                                                                                                                     | G                                 |                                                                      |  |  |

| 01                                                                                                                                       | s                                 | O₀                                                                   |  |  |

| S S                                                                                                                                      |                                   | $ - O_1 $                                                            |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                         |                                   | O 2011-2023 Feza BUZLUCA 5.16                                        |  |  |

| Digital Circuits                                                                                                                                                                           | License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                           |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

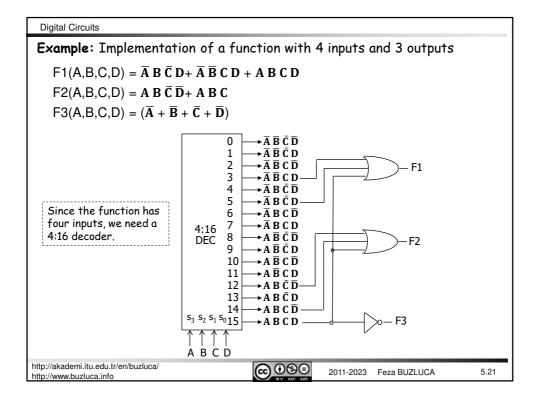

| Design of Logic Circuits                                                                                                                                                                   | Using Decoders:                                                                                                                                       |  |  |

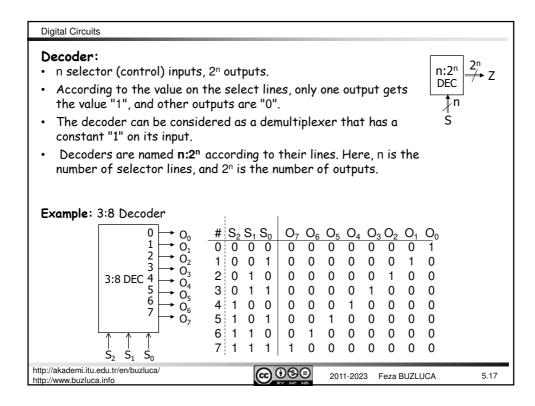

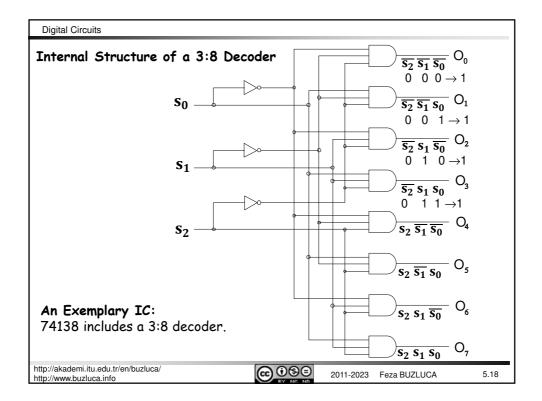

| Each possible input to the decoder can be considered as a minterm.                                                                                                                         |                                                                                                                                                       |  |  |

|                                                                                                                                                                                            | A decoder can be viewed as a " <b>minterm generator</b> " because each output is "1"<br>only when a particular minterm evaluates to "1" (Slide 5.18). |  |  |

| Remember that any logic expression can be represented as the sum (OR) of minterms, so it follows that we can implement any logical expression by ORing the related output(s) of a decoder. |                                                                                                                                                       |  |  |

| Method:                                                                                                                                                                                    |                                                                                                                                                       |  |  |

| A general logic circuit with n inputs and m outputs can be implemented by using only one n:2 <sup>n</sup> decoder and, in addition with OR gates.                                          |                                                                                                                                                       |  |  |

| <ul> <li>n inputs (variables) of the function are connected to the n select lines of the<br/>decoder.</li> </ul>                                                                           |                                                                                                                                                       |  |  |

| <ul> <li>Each output of a decoder</li> </ul>                                                                                                                                               | r corresponds to a minterm.                                                                                                                           |  |  |

| <ul> <li>The outputs of the decoder<br/>are added by using an OF</li> </ul>                                                                                                                | der, which correspond to the minterms of the function<br>R gate.                                                                                      |  |  |

|                                                                                                                                                                                            |                                                                                                                                                       |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                                                                           | 2011-2023 Feza BUZLUCA 5.19                                                                                                                           |  |  |

| Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| <b>Example:</b><br>Implement the given function $F(A,B,C)$ using a decoder and one OR gate.<br>$F(A,B,C) = \bigcup_1(0,2,6,7)$                                                                                                                                                                                                                                                                                                                                                |                                                                                                                |  |  |

| Solution:<br>As the function F(A,B,C) has three inputs, we need a 3-to-8 dec                                                                                                                                                                                                                                                                                                                                                                                                  | coder.                                                                                                         |  |  |

| $F(A,B,C) = \bigcup_{1}(0,2,6,7) = m0 + m2 + m6 + m7 = \overline{A} \overline{B} \overline{C} + \overline{A} I$                                                                                                                                                                                                                                                                                                                                                               | $\mathbf{B}\overline{\mathbf{C}} + \mathbf{A}\mathbf{B}\overline{\mathbf{C}} + \mathbf{A}\mathbf{B}\mathbf{C}$ |  |  |

| Always fully label all<br>inputs and outputs.<br>The boxes can be drawn<br>in different ways. $0 \rightarrow \overline{A} \ \overline{B} \ \overline{C}$<br>$2 \rightarrow \overline{A} \ \overline{B} \ \overline{C}$<br>$3:8 3 \rightarrow \overline{A} \ \overline{B} \ \overline{C}$<br>$DEC 4 \rightarrow \overline{A} \ \overline{B} \ \overline{C}$<br>$A \ \overline{B} \ \overline{C}$<br>$A \ \overline{B} \ \overline{C}$<br>$A \ \overline{B} \ \overline{C}$<br> | F                                                                                                              |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011-2023 Feza                                                                                                                                                                                                                                                                                                                                                                                               | BUZLUCA 5.20                                                                                                   |  |  |

| Digital Circuits                                                                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

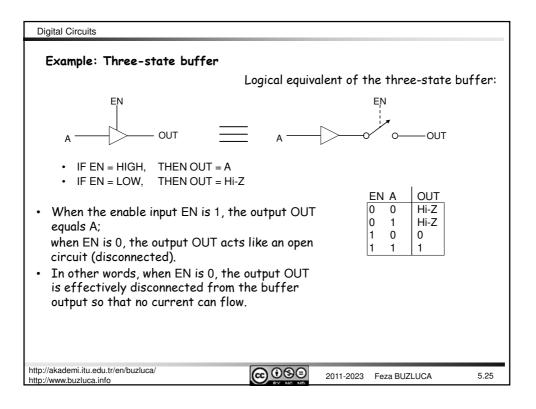

| Three-State Logic                                                                                                                                                      |  |  |

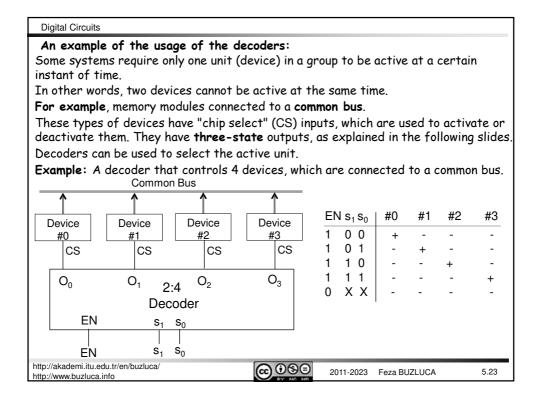

| Normally, the output of a logic device is in one of the two logic states, i.e., "0" or "1".                                                                            |  |  |

| Some logic devices are designed this way so their outputs can be in a <b>third state</b> .                                                                             |  |  |

| This is often referred to as a <b>Hi-Z (high-impedance)</b> state of the output because the circuit offers a very high resistance or impedance to the flow of current. |  |  |

| In this state, the output behaves like it is not connected to the circuit.                                                                                             |  |  |

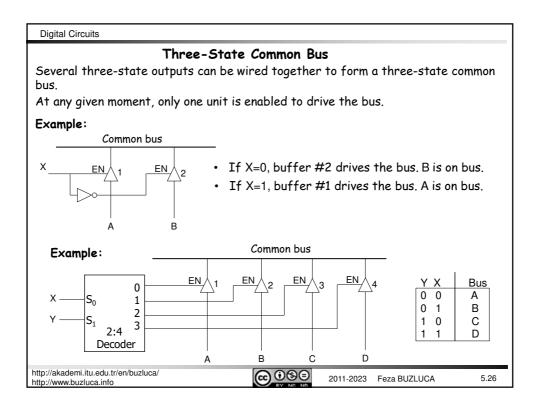

| The use of three-state logic permits the outputs of two or more gates or other logic devices to be connected together.                                                 |  |  |

| For example, the devices on slide 5.23 are designed to connect to a common bus.                                                                                        |  |  |

| When the chip select input of a device is not asserted, its output is in the third state.                                                                              |  |  |

| We will cover the implementation of the devices with three-state outputs in section 11, "Internal Structures of Electronic Digital Circuits."                          |  |  |

|                                                                                                                                                                        |  |  |

|                                                                                                                                                                        |  |  |

|                                                                                                                                                                        |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011-2023 Feza BUZLUCA 5.24                                                                           |  |  |