## Combinational Circuits As Building Blocks

Combinational logic circuits can perform commonly used operations (such as arithmetic operations, comparison, selection, decoding, etc.)

There exist corresponding logic structures (such as adders, multiplexers, and decoders) for performing these operations.

Instead of designing every complex function with basic logic gates, using these common structures makes the design simpler.

Their level of functionality often matches a designer's level of thinking when partitioning a large problem into smaller chunks (like functions in programming).

These structures can be interconnected to construct more extensive systems.

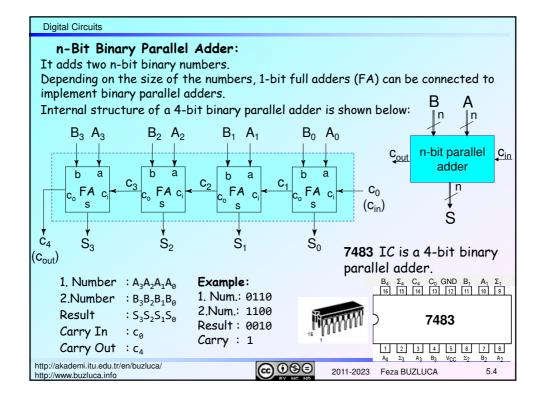

We design hardware using a hierarchical approach:

- We design a small component (e.g., a 1-bit adder) using basic logic gates.

- We build a large component by interconnecting many copies of the small component + a few extra gates (e.g., a 32-bit adder).

- We build chips by interconnecting many large components (e.g., a CPU).

- Each component is truly made out of many gates but using a hierarchy makes the design process faster and easier.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011-2023 Feza BUZLUCA

5.1

http://www.buzluca.info

**Digital Circuits**

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

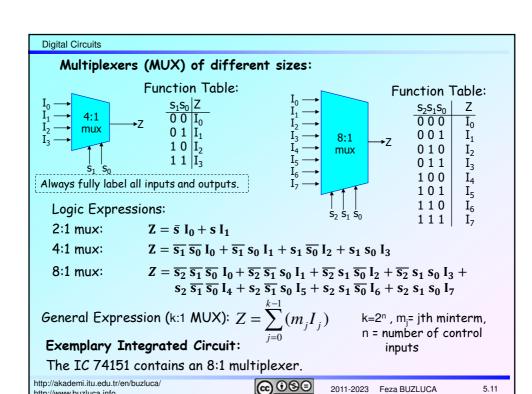

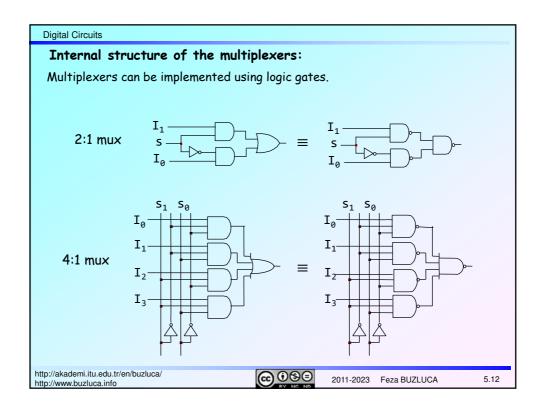

## Design of Logic Circuits Using Multiplexers 1:

A logic circuit with n inputs and one output can be implemented by using a single 2n:1 multiplexer and no other logic gates.

#### Method:

- The n inputs of the function (circuit) to be implemented are connected to the n selector lines of the multiplexer.

- Since each binary value of selector lines corresponds to an input combination, connect:

- "O" to data input lines corresponding to O-generating combinations, and

- "1" to data input lines corresponding to 1-generating combinations.

## Digital Circuits

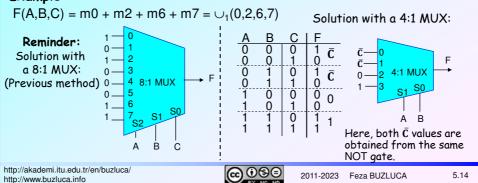

## Design of Logic Circuits Using Multiplexers 2:

A logic circuit with n inputs and one output can be implemented using a single  $2^{n-1}$ :1 multiplexer and a NOT gate.

### Method:

- Connect the n-1 inputs (variables) of the function to the n-1 select lines of the multiplexer.

- Then, connect the remaining single variable, or its complement, or 0, or 1 to the selection inputs of the multiplexer according to the values in the truth table.

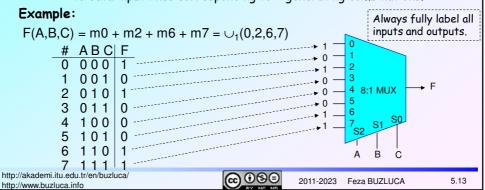

#### Example:

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

#### **Digital Circuits**

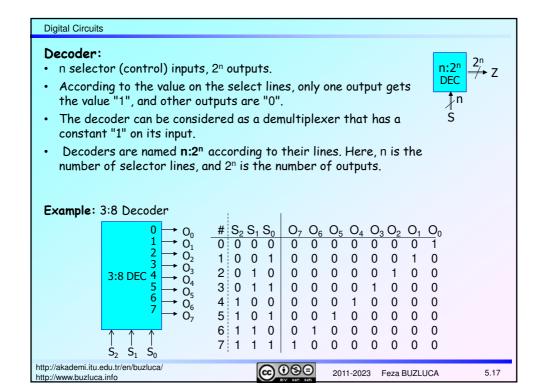

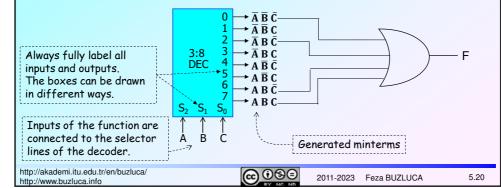

# Design of Logic Circuits Using Decoders:

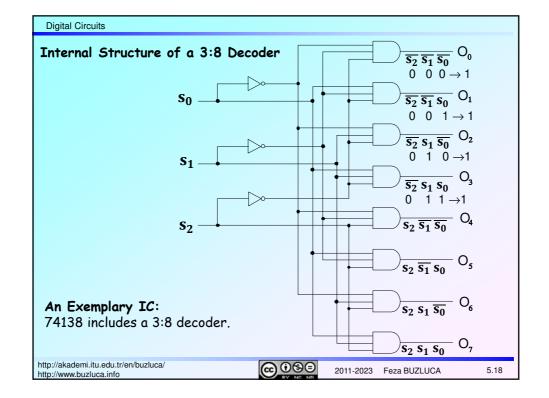

Each possible input to the decoder can be considered as a minterm.

A decoder can be viewed as a "minterm generator" because each output is "1" only when a particular minterm evaluates to "1" (Slide 5.18).

Remember that any logic expression can be represented as the sum (OR) of minterms, so it follows that we can implement any logical expression by ORing the related output(s) of a decoder.

### Method:

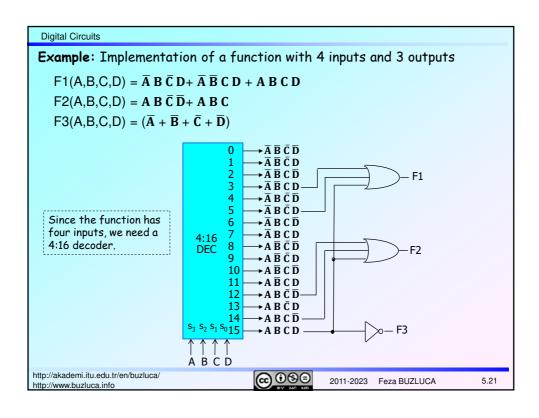

A general logic circuit with n inputs and m outputs can be implemented by using only one n:2<sup>n</sup> decoder and, in addition with OR gates.

- n inputs (variables) of the function are connected to the n select lines of the decoder.

- Each output of a decoder corresponds to a minterm.

- The outputs of the decoder, which correspond to the minterms of the function are added by using an OR gate.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011-2023 Feza BUZLUCA

5.19

### Digital Circuits

## Example:

Implement the given function F(A,B,C) using a decoder and one OR gate.

$$F(A,B,C) = \bigcup_{1}(0,2,6,7)$$

#### Solution:

As the function F(A,B,C) has three inputs, we need a 3-to-8 decoder.

$$F(A,B,C) = \bigcup_1(0,2,6,7) = m0 + m2 + m6 + m7 = \overline{A} \overline{B} \overline{C} + \overline{A} \overline{B} \overline{C} + A \overline{B} \overline{C} + A \overline{B} \overline{C}$$

**Digital Circuits**

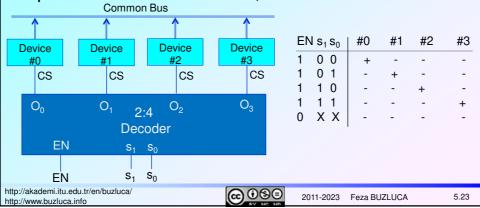

### An example of the usage of the decoders:

Some systems require only one unit (device) in a group to be active at a certain instant of time.

In other words, two devices cannot be active at the same time.

For example, memory modules connected to a common bus.

These types of devices have "chip select" (CS) inputs, which are used to activate or deactivate them. They have **three-state** outputs, as explained in the following slides. Decoders can be used to select the active unit.

**Example:** A decoder that controls 4 devices, which are connected to a common bus.

Digital Circuits

## Three-State Logic

Normally, the output of a logic device is in one of the two logic states, i.e., "0" or "1". Some logic devices are designed this way so their outputs can be in a **third state**.

This is often referred to as a Hi-Z (high-impedance) state of the output because the circuit offers a very high resistance or impedance to the flow of current.

In this state, the output behaves like it is not connected to the circuit.

The use of three-state logic permits the outputs of two or more gates or other logic devices to be connected together.

For example, the devices on slide 5.23 are designed to connect to a common bus.

When the chip select input of a device is not asserted, its output is in the third state.

We will cover the implementation of the devices with three-state outputs in section 11, "Internal Structures of Electronic Digital Circuits."

### Digital Circuits

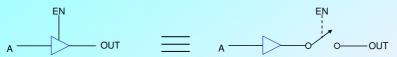

### Example: Three-state buffer

Logical equivalent of the three-state buffer:

- IF EN = HIGH, THEN OUT = A

- IF EN = LOW, THEN OUT = Hi-Z

- When the enable input EN is 1, the output OUT equals A;

when EN is 0, the output OUT acts like an open circuit (disconnected).

In other words, when EN is 0, the output OUT is effectively disconnected from the buffer output so that no current can flow.

| ΕN | Α | OUT  |

|----|---|------|

| 0  | 0 | Hi-Z |

| 0  | 1 | Hi-Z |

| 1  | 0 | 0    |

| 1  | 1 | 1    |

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011-2023 Feza BUZLUCA

5.25

## Digital Circuits

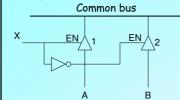

### Three-State Common Bus

Several three-state outputs can be wired together to form a three-state common bus

At any given moment, only one unit is enabled to drive the bus.

### Example:

- If X=0, buffer #2 drives the bus. B is on bus.

- If X=1, buffer #1 drives the bus. A is on bus.

####

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

@ <u>0</u>99

2011-2023 Feza BUZLUCA

5.26

Bus

Α

В

С

D