| Digital Circuits                                                                                                                                                                                      | gital Circuits License: https://creativecommons.org/licenses/by-nc-nd/4.0 |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|

| Programmable Logic Device (PLD)                                                                                                                                                                       |                                                                           |  |  |

| Today, complicated digital circuits are devices.                                                                                                                                                      | implemented using programmable logic                                      |  |  |

| These devices are integrated circuits that include many reconfigurable logic gates.<br>(From several hundred to several million).                                                                     |                                                                           |  |  |

| Some PLDs also include memory units (flip-flops).                                                                                                                                                     |                                                                           |  |  |

| The designer can reconfigure the connections between logic gates in the PLD using a programming language and a programming device.                                                                    |                                                                           |  |  |

| It is possible to implement complicated digital circuits with only a single IC (PLD).                                                                                                                 |                                                                           |  |  |

| There are different kinds of PLDs:                                                                                                                                                                    |                                                                           |  |  |

| <ul> <li>Programmable Logic Array - PLA</li> <li>Programmable Array Logic - PAL®</li> <li>Generic Array Logic - GAL</li> <li>Complex PLD - CPLD</li> <li>Field-Programmable Gate Array - F</li> </ul> | PAL is a registered trademark of Lattice Semiconductor<br>Corp.<br>PGA    |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                                                                                      | 2011-2023 Feza BUZLUCA 6.1                                                |  |  |

| Digital Circuits                                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Programming of PLDs:                                                                                                                                                                                                                                                                               |  |  |

| In early versions of PLDs (PLA, PAL), bipolar transistors were used (See Chapter 11)<br>They have fuses on the connection points between gates, which provide<br>reconfiguration (programming) of devices.<br>In these devices, fuses can be blown only once; therefore, they are called "one-time |  |  |

| programmable (OTP)."<br>Today's devices (GAL, CPLD, FPGA) are made of CMOS transistors and contain<br>memory units for programming.<br>They can be erased and reprogrammed many times.                                                                                                             |  |  |

| To program PLDs, various Hardware Description Languages (HDL) and programming devices are used.                                                                                                                                                                                                    |  |  |

| Some examples of HDLs: <ul> <li>PALASM</li> <li>ABEL</li> <li>Verilog</li> <li>VHDL (Very high speed integrated circuits HDL)</li> </ul>                                                                                                                                                           |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011-2023 Feza BUZLUCA 6.2                                                                                                                                                                                                        |  |  |

| Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Example: PAL16L8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| <ul> <li>Pins on the left side and side</li></ul> | Pins 12 and 19 can be used<br>only as outputs, but six of the<br>outputs (pins 13 to 18) are<br>also available as inputs via the<br>feedback line connection<br>after the inverting output<br>buffer.<br>This feature, called<br>programmable I/O, lets the<br>user program each of these<br>six pins as either input or<br>output. |  |  |  |

| <ul> <li>L signifies the output type, which is<br/>active low for this PAL part type.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2011-2023 Feza BUZLUCA 6.8                                                                                                                                                                                                                                                                                                          |  |  |  |

| Digital Circuits                                                                            |                                                   |             |  |  |

|---------------------------------------------------------------------------------------------|---------------------------------------------------|-------------|--|--|

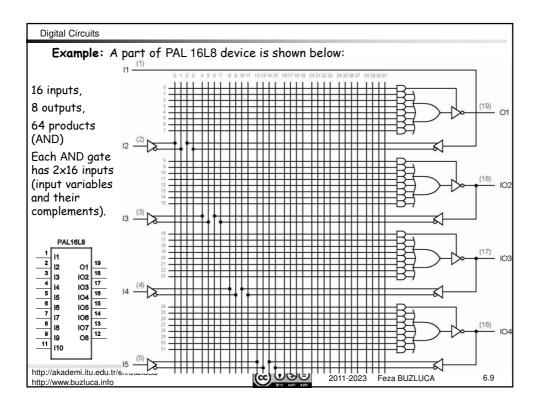

| Example: A part o                                                                           | Example: A part of PAL16L8 device is shown below: |             |  |  |

| • Eight AND 11 (1)<br>gates are<br>associated with<br>each output pin.                      |                                                   | (19)<br>O1  |  |  |

| <ul> <li>Seven of them<br/>provide inputs<br/>to a fixed 7-<br/>input OR gate.</li> </ul>   |                                                   |             |  |  |

| • The eighth<br>(called output-<br>enable gate) is<br>connected to <sup>13</sup>            |                                                   | (18)<br>IO2 |  |  |

| the three-<br>state enable<br>input of the<br>output buffer.                                |                                                   | (17)<br>IO3 |  |  |

| The buffer is<br>enabled only<br>when the<br>output-enable<br>gate has an<br>output of one. |                                                   | (16)<br>IO4 |  |  |

| http://akademi.itu.edu.tr/esuc.ucc                                                          | 2011-2023 Feza BUZLUCA                            | 6.10        |  |  |

| Digital Circuits                                                                                                          |                                      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|--|

|                                                                                                                           | mable Gate Array - FPGA              |  |  |  |

| It consists of an array of<br>configurable logic blocks (CLBs)                                                            |                                      |  |  |  |

| connected via programmable interconnects.                                                                                 |                                      |  |  |  |

| It can be erased and programmed many times.                                                                               |                                      |  |  |  |

| They contain several thousand to several million logic gates.                                                             |                                      |  |  |  |

| They can be used to implement complex digital circuits, e.g., special-                                                    |                                      |  |  |  |

| purpose microprocessors.<br>Compared to CPLDs, FPGAs are more<br>flexible and can implement more<br>complicated circuits. |                                      |  |  |  |

| However, the delay of FPGAs is higher.                                                                                    |                                      |  |  |  |

| Example:<br>AMD Artix™ UltraScale+™ AU25P                                                                                 | Switch and Configurable I/O          |  |  |  |

| 304 input/output pins<br>308000 system logic cells                                                                        | Connection Box Logic Block Block     |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                          | CO O O O 2011-2023 Feza BUZLUCA 6.12 |  |  |  |

| Digital Circuits                                                                                                                                                                      |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| ASIC (Application-specific integrated circuit)                                                                                                                                        |  |  |  |  |

| An application-specific integrated circuit (ASIC) is an integrated circuit (IC) designed for a particular use.                                                                        |  |  |  |  |

| An ASIC <u>is not</u> a reprogrammable device like an FPGA.                                                                                                                           |  |  |  |  |

| During the design of an ASIC, functional blocks are taken from a library, interconnected, and verified via simulation.                                                                |  |  |  |  |

| ASICs often include entire microprocessors, memory blocks, and other blocks for I/O operations. Such an ASIC is called a <b>SoC (system-on-chip)</b> .                                |  |  |  |  |

| HDLs are also used for designing ASICs, just like they are used for PLDs.                                                                                                             |  |  |  |  |

| ASIC are used in medical image processing, encoding/decoding data in communication devices, controlling the charging process in smartphones, etc.                                     |  |  |  |  |

| The non-recurring engineering (NRE) cost of an ASIC is very high.                                                                                                                     |  |  |  |  |

| <ul> <li>Non-recurring engineering (NRE) cost is the one-time cost to research,<br/>design, develop, and test a new product.</li> </ul>                                               |  |  |  |  |

| <ul> <li>Production costs must be paid constantly to maintain the production of a<br/>product.</li> </ul>                                                                             |  |  |  |  |

| Therefore, device manufacturers usually choose FPGAs for prototyping and low-<br>volume production, while ASICs are preferred for high-volume production with<br>amortized NRE costs. |  |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                 |  |  |  |  |

| HDI                                                                                                                                                                | -Based Design         |                              |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------|----------|

| It is difficult to design (des and logic functions.                                                                                                                | cribe) large and comp | blex systems using Boolea    | n algebr |

| Similar to software development, most digital design is now done at higher levels of abstraction.                                                                  |                       |                              |          |

| Software Design:                                                                                                                                                   |                       |                              |          |

| Although a CPU can only directly execute machine code, we do not use machine<br>language or assembly language for large systems unless absolutely necessary.       |                       |                              |          |

| We write complex programs using high-level programming languages such as C++,<br>Java, C#, and Python, which are closer to human language than to machine language |                       |                              |          |

| Compilers convert these programs to machine code.                                                                                                                  |                       |                              |          |

| Hardware Design:                                                                                                                                                   |                       |                              |          |

| Designers use Hardware Description Languages (HDLs) such as Verilog or VHDL to describe circuits at an abstract level. They do not have to use Boolean algebra.    |                       |                              |          |

| In addition, designers can ob<br>license from an intellectual p<br>circuit.                                                                                        |                       |                              |          |

| Finally, a Verilog or VHDL sy chip or programming an FPG/                                                                                                          |                       | luce a circuit by building c | ın ASI(  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                                                   | @ 080                 | 2011-2023 Feza BUZLUCA       | 6.14     |

| Digital Circui                          | its                             |                                                                                                                                                                                                 |  |  |

|-----------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                         |                                 | HDL-Based Design Flow                                                                                                                                                                           |  |  |

|                                         | Requirements<br>Functional      | • First, we identify the functional specifications of the required circuit.                                                                                                                     |  |  |

| l                                       | specifications                  | • Using a text editor, we write the program in an HDL, e.g.,<br>Verilog, that describes the specifications of the circuit.                                                                      |  |  |

|                                         | Coding<br>HDL                   | • The compiler creates a file in a digital-design description<br>language RTL (register-transfer language). The RTL file is<br>the description of the logic operations and<br>interconnections. |  |  |

|                                         | Compilation                     | • Using a simulation tool, we can verify if the designed circuit generates the expected outputs for given inputs.                                                                               |  |  |

|                                         | Simulation                      | • A synthesizer tool is used to target the RTL design to a specific hardware technology such as an ASIC, CPLD, or FPGA.                                                                         |  |  |

| Synthesizer                             |                                 | - Mapping the RTL design into hardware elements in the                                                                                                                                          |  |  |

|                                         | Mapping                         | target technology.                                                                                                                                                                              |  |  |

|                                         |                                 | <ul> <li>Placement of the necessary elements onto a physical<br/>chip layout.</li> </ul>                                                                                                        |  |  |

|                                         | Fitting                         | <ul> <li>Routing: Finding or creating paths between the inputs</li> <li>and outputs of placed elements.</li> </ul>                                                                              |  |  |

| and outputs of placed elements.         |                                 |                                                                                                                                                                                                 |  |  |

| ASIC                                    | CPLD                            | FPGA                                                                                                                                                                                            |  |  |

| http://akademi.itu<br>http://www.buzlue | u.edu.tr/en/buzluca/<br>ca.info | 2011-2023 Feza BUZLUCA 6.15                                                                                                                                                                     |  |  |

| Digital Circuits                                                                                                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Verilog                                                                                                                                                                                                                                                                 |  |  |  |

| Verilog is one of the popular hardware description languages.                                                                                                                                                                                                           |  |  |  |

| The other one is VHDL.                                                                                                                                                                                                                                                  |  |  |  |

| The syntax of Verilog is similar to that of the C programming language.                                                                                                                                                                                                 |  |  |  |

| Standards:                                                                                                                                                                                                                                                              |  |  |  |

| Verilog-2001: IEEE standard 1364-2001.                                                                                                                                                                                                                                  |  |  |  |

| <ul> <li>Verilog-2005: IEEE standard 1364-2005.</li> </ul>                                                                                                                                                                                                              |  |  |  |

| <ul> <li>System Verilog: IEEE standard 1800-2009.</li> </ul>                                                                                                                                                                                                            |  |  |  |

| The 2009 standard, System Verilog, includes Verilog-2001/2005 as a subset and introduces new features for specifying, designing, and verifying complex systems.                                                                                                         |  |  |  |

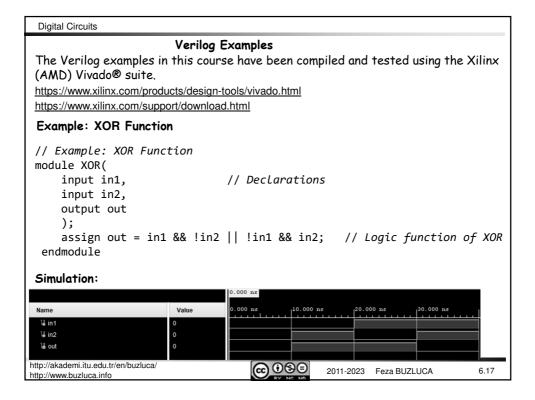

| The basic unit of design and programming in Verilog is a <b>module</b> .<br>A module may correspond to a single piece of hardware.<br>Modules are similar to functions or procedures in programming.<br>Modules can be used as building blocks in other larger modules. |  |  |  |

| A Verilog module consists of declarations and statements.                                                                                                                                                                                                               |  |  |  |

| Declarations describe the names and types of the module's inputs and outputs, as well as local signals, variables, and constants used internally in the module.                                                                                                         |  |  |  |

| The statements specify or "model" the operation of the module's outputs and internal signals.                                                                                                                                                                           |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011-2023 Feza BUZLUCA 6.16                                                                                                                                                                            |  |  |  |

|                                                                                                                                                                                                                                                                         |  |  |  |

| Digital Circuits                                                                                 |                                  |                                         |                   |  |

|--------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------|-------------------|--|

| Example: Full Adder                                                                              | using XOR Module                 | Full A                                  | dder: Slide 5.3   |  |

| <pre>// Example: Full Ad<br/>module FullAdder(</pre>                                             |                                  |                                         |                   |  |

| ,                                                                                                | // First number                  | <b>,</b>                                |                   |  |

|                                                                                                  | // Second numbe                  | 2r                                      |                   |  |

|                                                                                                  | // Carry input                   |                                         |                   |  |

| output Cout                                                                                      | // Output Sum<br>// Carry output | :                                       |                   |  |

| );<br>wire x;                                                                                    | // Internal wir                  | re                                      |                   |  |

| <pre>// We use the XOR module designed in advance<br/>XOR XOR1(.in1(a), .in2(b), .out(x));</pre> |                                  |                                         |                   |  |

|                                                                                                  |                                  | Example:<br>FullAdder.v<br>Adder_Test.v |                   |  |

| http://akademi.itu.edu.tr/en/buzluca<br>http://www.buzluca.info                                  | í e                              | 000 2011-2023                           | Feza BUZLUCA 6.18 |  |