| Digital Circuits                                                                                                                                                                                                 | License: https://creativecommons.org/licenses/by-nc-nd/4.0/ |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|

| SEQUENTIAL CIRCUITS                                                                                                                                                                                              |                                                             |  |  |  |

| <ul> <li>In the first part of the course, combinational circuits were covered.<br/>The outputs of combinational circuits depend only on current inputs.<br/>Combinational circuit: Output = G (Input)</li> </ul> |                                                             |  |  |  |

| <ul> <li>In sequential circuits, the outputs depend both on the inputs and the "state" of<br/>the circuit.</li> </ul>                                                                                            |                                                             |  |  |  |

| Sequential circuit: Output = G (Input , Current State)                                                                                                                                                           |                                                             |  |  |  |

| Next State = H (Input , Current State)                                                                                                                                                                           |                                                             |  |  |  |

| <b>Memory</b> units are required to store (remember) the state of the circuit.                                                                                                                                   |                                                             |  |  |  |

| For example, a vending machine keeps track of (remembers) the coins inserted into the machine.                                                                                                                   |                                                             |  |  |  |

| With each coin, the state of the machine (the total amount of money corresponding to the inserted coins) is updated.                                                                                             |                                                             |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                                                                                                                                                 | 2011 - 2023 Feza BUZLUCA 8.1                                |  |  |  |

| Digital Circuits                                                                                                 |                              |  |  |

|------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

| Types of sequential circuits:                                                                                    |                              |  |  |

| There are two types of sequential circuits :                                                                     |                              |  |  |

| A) Synchronous sequential circuits:                                                                              |                              |  |  |

| • Their states can change at a discrete instant of t                                                             | time.                        |  |  |

| • All memory elements are synchronized by a comm                                                                 | ion <b>clock signal</b> .    |  |  |

| <ul> <li>Therefore, these circuits are also called "clocked synchronous sequential"<br/>circuits.</li> </ul>     |                              |  |  |

| B) Asynchronous sequential circuit:                                                                              |                              |  |  |

| • Their state can change at any instant of time dep                                                              | pending upon the input signa |  |  |

| In this course, we will deal only with clocked synchrobic because nearly all sequential logic today is clocked s |                              |  |  |

| For example, microprocessors are clocked synchron                                                                | ous sequential circuits.     |  |  |

|                                                                                                                  |                              |  |  |

|                                                                                                                  |                              |  |  |

| http://akademi.itu.edu.tr/en/buzluca/                                                                            | 2011 - 2023 Feza BUZLUCA 8,2 |  |  |

Digital Circuits

## Finite State Machine (FSM) Model

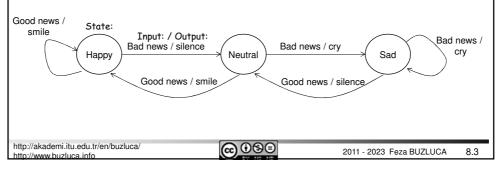

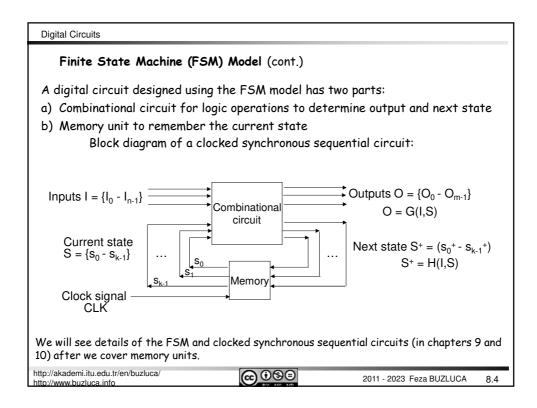

Sequential circuits are designed using the "finite state machine - FSM" model. This model is also used in the design of many other systems.

An FSM has inputs, states, and outputs.

- When the machine is started, it is in a specific state (initial state:  $s_{\scriptscriptstyle 0}).$

- An output is produced depending on the inputs and the current state.  $\mathsf{O}=\mathsf{G}\left(\mathsf{I},\mathsf{S}\right)$

- Transition into a new state occurs depending on the input and the current state. To illustrate the behavior of an FSM, state/output diagrams are used.

**Example**: A state/output diagram for an FSM that models the behavior of a human

| Digital Circuits                                                                                                 |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Memory Units                                                                                                     |  |  |  |  |

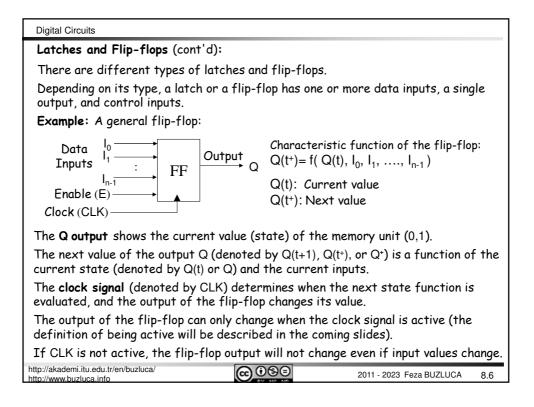

| Latches and Flip-flops:                                                                                          |  |  |  |  |

| A basic memory cell is a circuit that stores <b>one bit</b> of information for as long as the device is powered. |  |  |  |  |

| This one-bit memory element is called a flip-flop or a latch because it latches (or<br>locks) data in it.        |  |  |  |  |

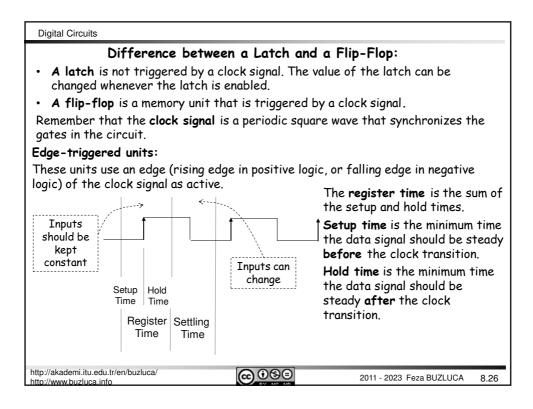

| A memory element that has no clock input is often called a <b>latch</b> .                                        |  |  |  |  |

| It is not triggered by a control signal (i.e., a clock signal).                                                  |  |  |  |  |

| The value of the latch can be changed whenever the latch is enabled.                                             |  |  |  |  |

| A <b>flip-flop</b> is a memory unit that is triggered by a <b>clock signal</b> .                                 |  |  |  |  |

| In this chapter, we will cover the details of latches and flip-flops.                                            |  |  |  |  |

|                                                                                                                  |  |  |  |  |

|                                                                                                                  |  |  |  |  |

|                                                                                                                  |  |  |  |  |

|                                                                                                                  |  |  |  |  |

|                                                                                                                  |  |  |  |  |

|                                                                                                                  |  |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011 - 2023 Feza BUZLUCA 8.5                    |  |  |  |  |

| Digital Circuits                                                                       | License: https://creative    | commons.org/licenses/by-nc-nd/4.0/                             |  |

|----------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------|--|

| Clock Signal:                                                                          |                              | t <sub>H</sub> t <sub>L</sub><br> ←→→  ←→→                     |  |

| The clock signal is a periodic synchronizes the gates in the                           |                              |                                                                |  |

| A logic unit that has a clock si signal is active. If the clock s                      |                              | is enabled only when the clock<br>ip-flop preserves its state. |  |

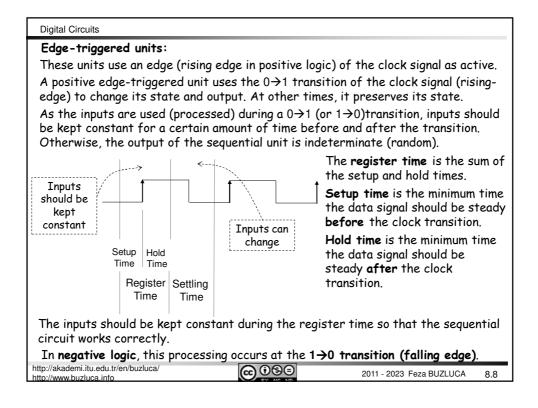

| There are two types of units                                                           | that differ in how they u    | use the clock signal:                                          |  |

| a) Level-triggered un                                                                  | its b) Edge-trigg            | gered units                                                    |  |

| Level-triggered units use a level of the clock signal (1 in positive logic) as active. |                              |                                                                |  |

| A level-triggered unit become<br>at the <b>high</b> level.                             | s active and changes its     | output when the clock signal is                                |  |

| It preserves its state when the                                                        | ne clock signal is at the le | ow level.                                                      |  |

| When the clock signal is at th are being processed.                                    | e high level ("1"), the inp  | outs should not change as they                                 |  |

| Otherwise, the output of the indeterminate (random).                                   | sequential circuit is        |                                                                |  |

| This time is called the <b>registe</b>                                                 | er time.                     | Settling Register                                              |  |

| The inputs can change when t<br>time is called the <b>settling tim</b>                 |                              | time Time                                                      |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info                       | 080                          | 2011 - 2023 Feza BUZLUCA 8.7                                   |  |

| Digital Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

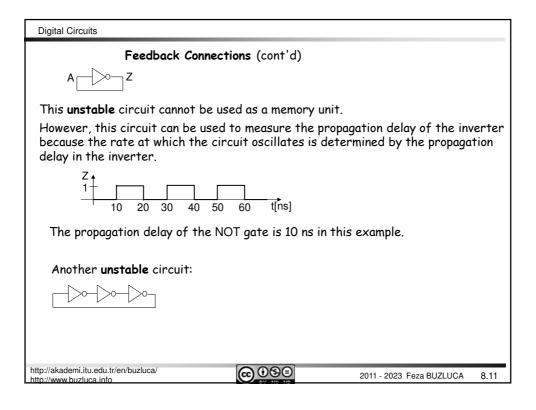

| Feedback Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| The combinational circuits we have studied so far have not had feedback connections. To construct a circuit that has memory, we must introduce feedback into the circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| By <b>feedback</b> , we mean that the output of one of the gates is connected back to the input of another gate in the circuit to form a closed loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Example:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| If, at some instant of time, the inverter input A is "0", this "0" will propagate through the inverter and cause the output Z to become "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| This "1" is fed back into the input, so after the propagation delay, the inverter output Z will become "0".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| When this 0 feeds back into the input A, the output Z will again switch to "1", and so forth.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Inverter output Z will continue to oscillate back and forth between "0" and "1" as shown in the figure below, and it will never reach a stable condition (it will remain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| unstable). Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 10         20         30         40         50         60         t[ns]           http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info         Image: Comparison of the second |  |  |  |

| Digital Circuits                                                                                                                                                                                                                                                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

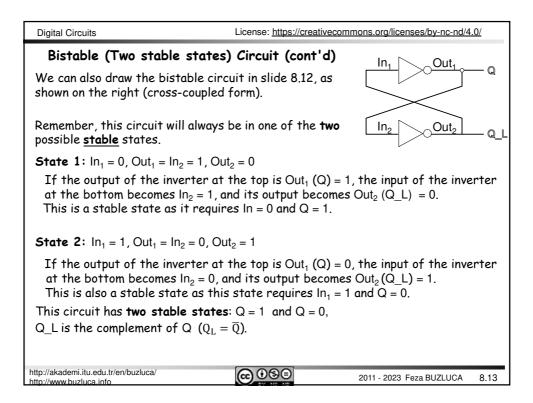

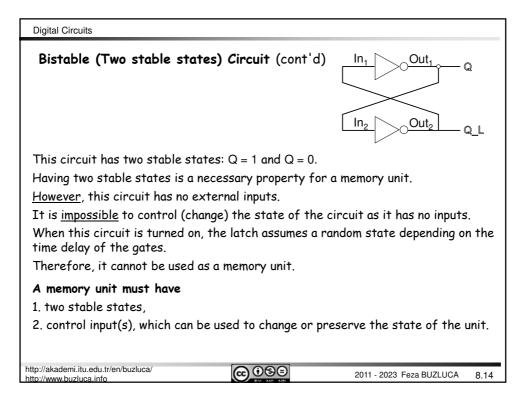

| Feedback Loop with Two Inverters (Bistable Circuit)                                                                                                                                                                                                                                                    |  |  |  |

| Next, consider a feedback loop with two inverters, shown below.<br>In this case, the circuit has <u>two stable</u> conditions ( <u>bistable</u> ), often referred to<br>as stable states.                                                                                                              |  |  |  |

| Stable state 1:<br>0 1 1<br>In1 Out1 In2 Out2                                                                                                                                                                                                                                                          |  |  |  |

| If the input to the first inverter is 0, its output will be 1.<br>Then, the input to the second inverter will be 1, and its output will be 0.<br>This 0 will feed back into the first inverter, but since this input is already 0, no<br>changes will occur.<br>The circuit is then in a stable state. |  |  |  |

| Stable state 2:<br>1 0 0 1<br>In1 Out1 In2 Out2                                                                                                                                                                                                                                                        |  |  |  |

| A second stable state of the circuit occurs when the input to the first inverter is 1 and the input to the second inverter is 0.                                                                                                                                                                       |  |  |  |

| Ittp://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                                                                                                                  |  |  |  |

| Digital Circuits                                                                                                              |     |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

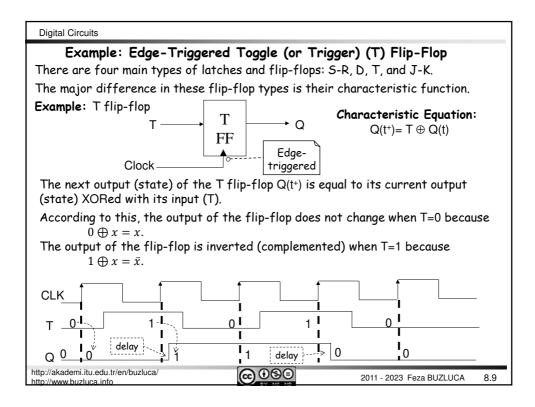

| Edge-Triggered Toggle (T) Flip-Flop                                                                                           |     |  |  |  |

| An edge-triggered T flip-flop can be implemented using an edge-triggered D flip-                                              |     |  |  |  |

| flop and an XOR gate.                                                                                                         |     |  |  |  |

| $T \longrightarrow T \longrightarrow Q$                                                                                       |     |  |  |  |

| $ \begin{array}{c} \downarrow \\ \neg \\$                     |     |  |  |  |

|                                                                                                                               |     |  |  |  |

| If the input is $0(T, 0)$ the value of the flip flep is preserved as $0 = 0$                                                  |     |  |  |  |

| If the input is 0 (T=0), the value of the flip-flop is preserved as $0 \oplus Q = Q$ .<br>$T = 0 \rightarrow Q(t + 1) = Q(t)$ |     |  |  |  |

| If the input is 1 (T=1), the value of the flip-flop is complemented (toggled) becau                                           | ise |  |  |  |

| $1 \oplus Q = Q.$<br>$T = 1 \rightarrow O(t+1) = \overline{O(t)}$ Characteristic Fauation: $O(t+1) = T \oplus O(t)$           |     |  |  |  |

| $T = 1 \rightarrow Q(t+1) = Q(t)$ Characteristic Equation: $Q(t+1) = T \oplus Q(t)$                                           |     |  |  |  |

|                                                                                                                               |     |  |  |  |

|                                                                                                                               |     |  |  |  |

| <b>-</b>                                                                                                                      |     |  |  |  |

|                                                                                                                               |     |  |  |  |

| Q                                                                                                                             |     |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                         | .34 |  |  |  |

| nuructeristic c | quano  | ns of Latches and Flip-F                                                            | loha     |  |

|-----------------|--------|-------------------------------------------------------------------------------------|----------|--|

| haracteristic e | quatio | r of a latch or flip-flop ca<br>n that specifies the next<br>its and current state. |          |  |

| Charact         | eristi | c equations of flip-flops                                                           | s:       |  |

| S-R FF          | :      | $Q(t+1) = S + \overline{R} \bullet Q(t)$                                            | (SR = 0) |  |

| J-K FF          | :      | $Q(t+1) = J \bullet \overline{Q(t)} + \overline{K} \bullet 0$                       | Q(t)     |  |

| D FF            | :      | Q(t+1) = D                                                                          |          |  |

| T FF            | :      | $Q(t{+}1)=T\oplus\ Q(t)$                                                            |          |  |

|                 |        |                                                                                     |          |  |

|                 |        |                                                                                     |          |  |

|                 |        |                                                                                     |          |  |

|                 |        |                                                                                     |          |  |

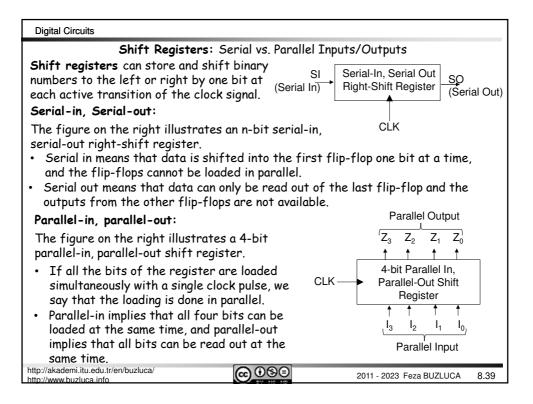

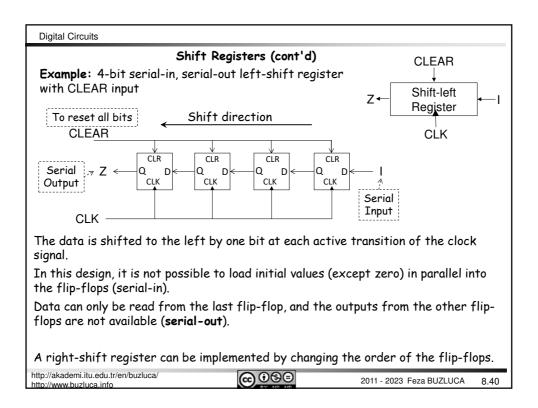

| Digital Circuits                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

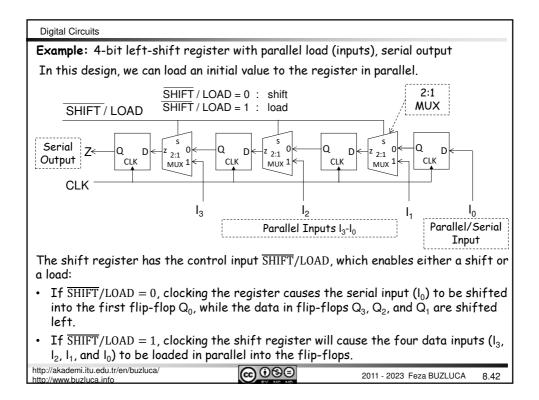

| Shift Register Configurations                                                                                                                                                                                                  |  |  |  |  |

| Four register configurations (the combinations resulting from a choice of parallel or serial for the inputs and the outputs) are possible:                                                                                     |  |  |  |  |

| <ul> <li>Parallel-in, Parallel-out</li> </ul>                                                                                                                                                                                  |  |  |  |  |

| <ul> <li>Serial-in, Serial-out</li> </ul>                                                                                                                                                                                      |  |  |  |  |

| <ul> <li>Parallel-in, Serial-out</li> </ul>                                                                                                                                                                                    |  |  |  |  |

| <ul> <li>Serial-in, Parallel-out</li> </ul>                                                                                                                                                                                    |  |  |  |  |

| <ul> <li>Shift Register Applications</li> <li>Many computers operate on parallel data, but this data must sometimes be converted to serial format to be sent.</li> </ul>                                                       |  |  |  |  |

| <ul> <li>Throughout most of the history of personal computers, data has been<br/>transferred through serial ports to devices such as modems, terminals, and<br/>various peripherals and directly between computers.</li> </ul> |  |  |  |  |

| <ul> <li>ICs called UARTs (universal asynchronous receiver-transmitters) are used to<br/>interface microprocessors and parallel data to communications links that use<br/>serial data.</li> </ul>                              |  |  |  |  |

| <ul> <li>Shift registers can perform this parallel-to-serial conversion and serial-to-<br/>parallel conversion.</li> </ul>                                                                                                     |  |  |  |  |

| <ul> <li>Shift registers are available in IC form or can be constructed from discrete<br/>flip-flops.</li> </ul>                                                                                                               |  |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info 2011 - 2023 Feza BUZLUCA 8.41                                                                                                                                 |  |  |  |  |

| Digital Circuits                                                        | License: <u>https://creativecommons.org/</u>                          | licenses/by-nc-nd/4.0/                               |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------------------------------------|

| Example: 74164 8-Bit Serial-I                                           | In Parallel-Out Shift Register                                        |                                                      |

| Serial data is entered through<br>synchronous with the LOW-to<br>(CLK). |                                                                       | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

| This register does not have pa outputs).                                | arallel load capability ( $Q_7$ - $Q_0$ are                           | 6 [ Q <sub>2</sub>                                   |

|                                                                         | ronous Master Reset (MR'), which<br>ng all outputs to LOW independent |                                                      |

| For details, you may refer to t                                         | the datasheet of the device.                                          |                                                      |

|                                                                         |                                                                       |                                                      |

|                                                                         |                                                                       |                                                      |

|                                                                         |                                                                       |                                                      |

| http://akademi.itu.edu.tr/en/buzluca/<br>http://www.buzluca.info        | <b>© 0SE</b> 2011 - 20                                                | 23 Feza BUZLUCA 8.43                                 |