License: https://creativecommons.org/licenses/by-nc-nd/4.0/

# SEQUENTIAL CIRCUITS

• In the first part of the course, combinational circuits were covered.

The outputs of combinational circuits depend only on current inputs.

Combinational circuit: Output = G (Input)

• In **sequential circuits**, the outputs depend both on the inputs and the "state" of the circuit.

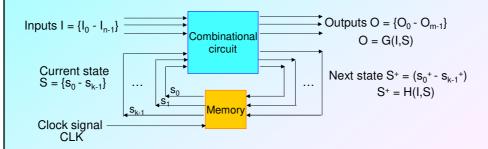

Sequential circuit: Output = G (Input , Current State)

Next State = H (Input , Current State)

Memory units are required to store (remember) the state of the circuit.

For example, a vending machine keeps track of (remembers) the coins inserted into the machine.

With each coin, the state of the machine (the total amount of money corresponding to the inserted coins) is updated.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.1

### Digital Circuits

# Types of sequential circuits:

There are two types of sequential circuits:

- A) Synchronous sequential circuits:

- · Their states can change at a discrete instant of time.

- All memory elements are synchronized by a common clock signal.

- Therefore, these circuits are also called "clocked synchronous sequential" circuits.

- B) Asynchronous sequential circuit:

- Their state can change at any instant of time depending upon the input signals.

In this course, we will deal only with clocked synchronous sequential circuits because nearly all sequential logic today is clocked synchronous.

For example, microprocessors are clocked synchronous sequential circuits.

### Finite State Machine (FSM) Model

Sequential circuits are designed using the "finite state machine - FSM" model.

This model is also used in the design of many other systems.

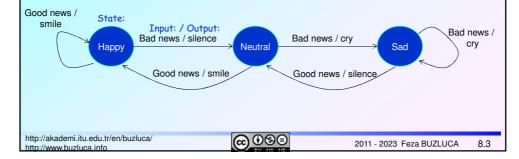

An FSM has inputs, states, and outputs.

- When the machine is started, it is in a specific state (initial state:  $s_0$ ).

- An output is produced depending on the inputs and the current state. O = G(I,S)

- Transition into a new state occurs depending on the input and the current state.

To illustrate the behavior of an FSM, state/output diagrams are used.

Example: A state/output diagram for an FSM that models the behavior of a human

### Digital Circuits

### Finite State Machine (FSM) Model (cont.)

A digital circuit designed using the FSM model has two parts:

- a) Combinational circuit for logic operations to determine output and next state

- b) Memory unit to remember the current state

Block diagram of a clocked synchronous sequential circuit:

We will see details of the FSM and clocked synchronous sequential circuits (in chapters 9 and 10) after we cover memory units.

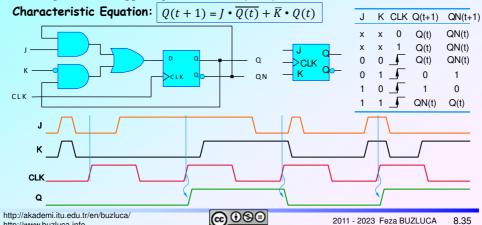

### **Memory Units**

### Latches and Flip-flops:

A basic memory cell is a circuit that stores **one bit** of information for as long as the device is powered.

This one-bit memory element is called a flip-flop or a latch because it latches (or locks) data in it.

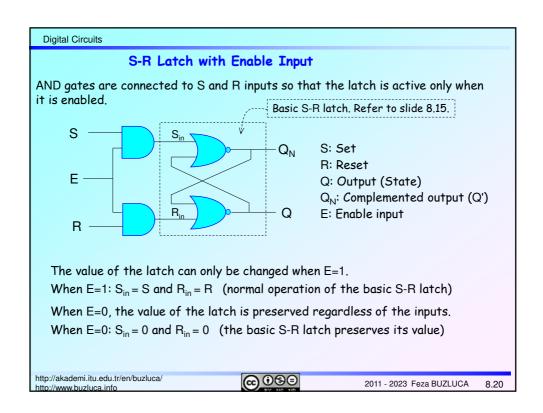

A memory element that has no clock input is often called a latch.

It is not triggered by a control signal (i.e., a clock signal).

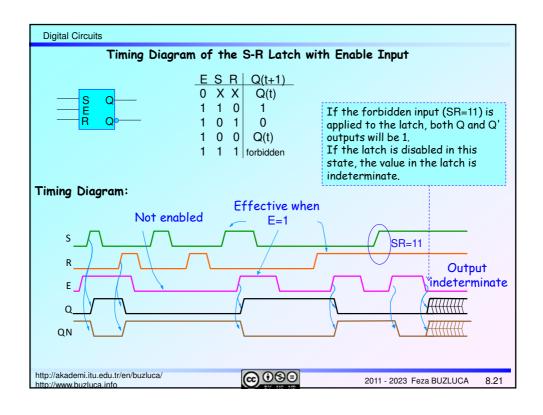

The value of the latch can be changed whenever the latch is enabled.

A flip-flop is a memory unit that is triggered by a clock signal.

In this chapter, we will cover the details of latches and flip-flops.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.5

# Digital Circuits

Clock (CLK)

### Latches and Flip-flops (cont'd):

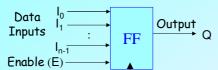

There are different types of latches and flip-flops.

Depending on its type, a latch or a flip-flop has one or more data inputs, a single output, and control inputs.

**Example:** A general flip-flop:

Characteristic function of the flip-flop:

$Q(t^+)=f(Q(t), I_0, I_1, ..., I_{n-1})$

Q(t): Current value Q(t+): Next value

The Q output shows the current value (state) of the memory unit (0,1).

The next value of the output Q (denoted by Q(t+1),  $Q(t^*)$ , or  $Q^*$ ) is a function of the current state (denoted by Q(t) or Q) and the current inputs.

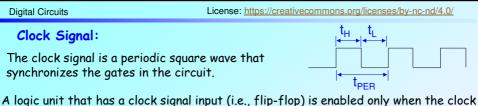

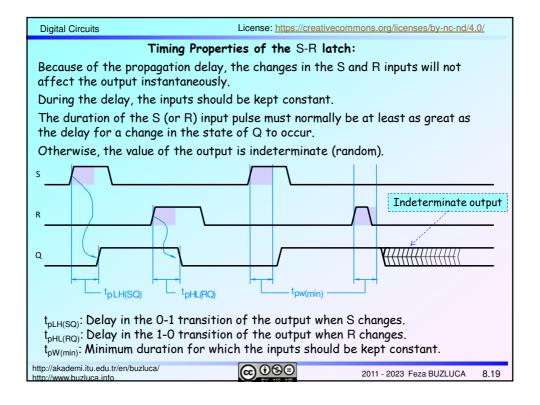

The clock signal (denoted by CLK) determines when the next state function is evaluated, and the output of the flip-flop changes its value.

The output of the flip-flop can only change when the clock signal is active (the definition of being active will be described in the coming slides).

If CLK is not active, the flip-flop output will not change even if input values change.

signal is active. If the clock signal is not active, the flip-flop preserves its state.

There are two types of units that differ in how they use the clock signal:

a) Level-triggered units

b) Edge-triggered units

Level-triggered units use a level of the clock signal (1 in positive logic) as active.

A level-triggered unit becomes active and changes its output when the clock signal is at the **high** level.

It preserves its state when the clock signal is at the low level.

When the clock signal is at the high level ("1"), the inputs should not change as they are being processed.

Otherwise, the output of the sequential circuit is indeterminate (random).

This time is called the register time.

The inputs can change when the clock signal is 0. This time is called the settling time.

Settling Register time Time

http://akademi.itu.edu.tr/en/buzluca/ ttp://www.buzluca.info

@ ⊕ ⊕

2011 - 2023 Feza BUZLUCA 8.7

### Digital Circuits

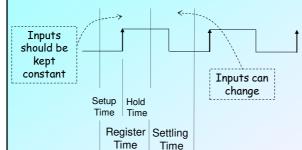

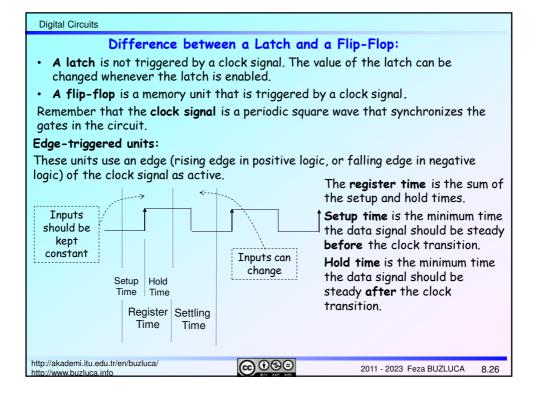

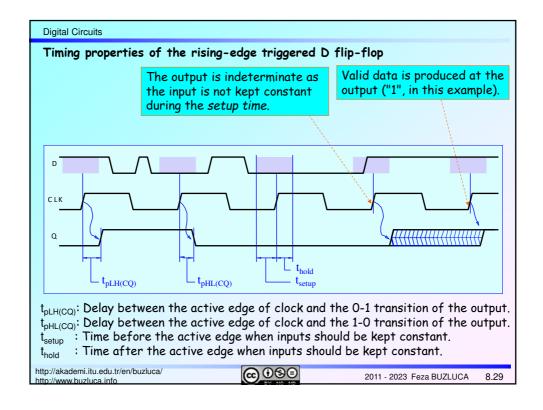

### Edge-triggered units:

These units use an edge (rising edge in positive logic) of the clock signal as active. A positive edge-triggered unit uses the 0-1 transition of the clock signal (risingedge) to change its state and output. At other times, it preserves its state.

As the inputs are used (processed) during a  $0 \rightarrow 1$  (or  $1 \rightarrow 0$ ) transition, inputs should be kept constant for a certain amount of time before and after the transition. Otherwise, the output of the sequential unit is indeterminate (random).

The register time is the sum of the setup and hold times.

Setup time is the minimum time the data signal should be steady before the clock transition.

Hold time is the minimum time the data signal should be steady **after** the clock transition.

The inputs should be kept constant during the register time so that the sequential circuit works correctly.

In negative logic, this processing occurs at the 1 $\rightarrow$ 0 transition (falling edge).

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

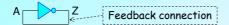

### Feedback Connections

The combinational circuits we have studied so far have not had feedback connections. To construct a circuit that has memory, we must introduce feedback into the circuit.

By **feedback**, we mean that the output of one of the gates is connected back to the input of another gate in the circuit to form a closed loop.

### Example:

If, at some instant of time, the inverter input A is "0", this "0" will propagate through the inverter and cause the output Z to become "1".

This "1" is fed back into the input, so after the propagation delay, the inverter output Z will become "0".

When this O feeds back into the input A, the output Z will again switch to "1", and so forth.

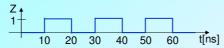

Inverter output Z will continue to oscillate back and forth between "0" and "1" as shown in the figure below, and it will never reach a stable condition (it will remain unstable).

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info @ ① § <del>=</del>

2011 - 2023 Feza BUZLUCA

### Feedback Connections (cont'd)

This unstable circuit cannot be used as a memory unit.

However, this circuit can be used to measure the propagation delay of the inverter because the rate at which the circuit oscillates is determined by the propagation delay in the inverter.

The propagation delay of the NOT gate is 10 ns in this example.

Another unstable circuit:

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.11

Digital Circuits

### Feedback Loop with Two Inverters (Bistable Circuit)

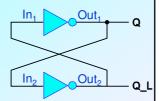

Next, consider a feedback loop with two inverters, shown below.

In this case, the circuit has  $\underline{\text{two stable}}$  conditions ( $\underline{\text{bistable}}$ ), often referred to as stable states.

Stable state 1:

If the input to the first inverter is 0, its output will be 1.

Then, the input to the second inverter will be 1, and its output will be 0.

This 0 will feed back into the first inverter, but since this input is already 0, no changes will occur.

The circuit is then in a stable state.

Stable state 2:

A second stable state of the circuit occurs when the input to the first inverter is 1 and the input to the second inverter is 0.

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

### Bistable (Two stable states) Circuit (cont'd)

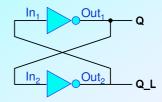

We can also draw the bistable circuit in slide 8.12, as shown on the right (cross-coupled form).

Remember, this circuit will always be in one of the **two** possible **stable** states.

**State 1:**

$$In_1 = 0$$

,  $Out_1 = In_2 = 1$ ,  $Out_2 = 0$

If the output of the inverter at the top is  $Out_1$  (Q) = 1, the input of the inverter at the bottom becomes  $In_2 = 1$ , and its output becomes  $Out_2$  (Q\_L) = 0. This is a stable state as it requires In = 0 and Q = 1.

**State 2:**

$$In_1 = 1$$

,  $Out_1 = In_2 = 0$ ,  $Out_2 = 1$

If the output of the inverter at the top is  $Out_1(Q) = 0$ , the input of the inverter at the bottom becomes  $In_2 = 0$ , and its output becomes  $Out_2(Q_L) = 1$ .

This is also a stable state as this state requires  $ln_1 = 1$  and Q = 0.

This circuit has two stable states: Q = 1 and Q = 0,

Q\_L is the complement of Q ( $Q_L = \overline{Q}$ ).

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.13

**Digital Circuits**

Bistable (Two stable states) Circuit (cont'd)

This circuit has two stable states: Q = 1 and Q = 0.

Having two stable states is a necessary property for a memory unit.

However, this circuit has no external inputs.

It is <u>impossible</u> to control (change) the state of the circuit as it has no inputs.

When this circuit is turned on, the latch assumes a random state depending on the time delay of the gates.

Therefore, it cannot be used as a memory unit.

### A memory unit must have

- 1. two stable states,

- 2. control input(s), which can be used to change or preserve the state of the unit.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2023 Feza BUZLUCA

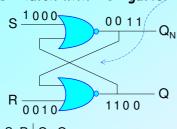

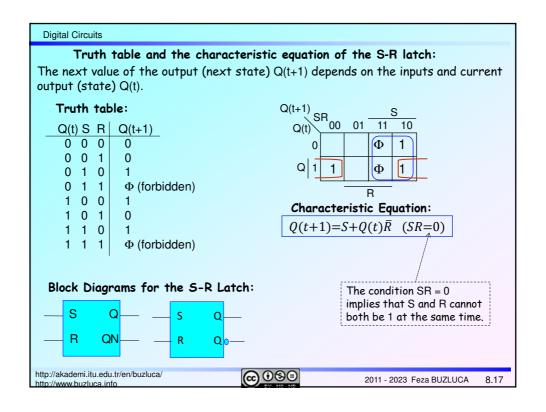

### S-R (Set-Reset) Latch

The S-R latch is a one-bit memory device constructed by introducing feedback into a circuit with two NOR (or NAND) gates.

All other latches and flip-flops can be built from this fundamental memory device by adding external gates.

To emphasize the symmetry between the operation

S: Set

R: Reset

# S-R latch with NOR gates:

| S | R | Q                                                      | Qu |                 |

|---|---|--------------------------------------------------------|----|-----------------|

| 1 | 0 | 1                                                      | 0  | _               |

| 0 | 0 | 1                                                      | 0  | After S=1, R=0  |

| 0 | 1 | 0                                                      | 1  | , ,             |

| 0 | 0 | 0                                                      | 1  | After S=0, R=1  |

| 1 | 1 | 0                                                      | 0  | Forbidden input |

|   |   | ${\sf Q}$ and ${\sf Q}_{\sf N}$ should be complements! |    |                 |

Q: Output (State)  $Q_N$ : Complemented output  $Q_{NOT}(\bar{Q})$

Recall: For a NOR gate,

When one of the inpute is "1" the

When one of the inputs is "1", the output will be "0" regardless of the other input.

of the two gates, the circuit is often drawn in "cross-coupled" form.

- The output is "1" only when both inputs are "0".

- The input S is used to write (store) a "1" to the latch (an input S=1 "sets" the output to Q=1).

- The input R is used to write a "0" (an input R = 1 "resets" the output to Q=0).

- If both inputs are "0", the S-R latch preserves its state.

- Both inputs should not be "1" at the same time.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8 15

# Digital Circuits

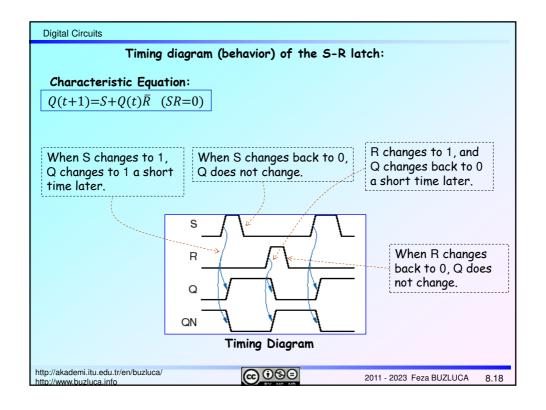

### State Changes of the S-R (Set-Reset) Latch

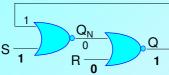

To show how states of an S-R latch change, we can draw the circuits:

### S=1, R=0 / Q=1:

If S=1, R=0,  $Q_N$  will be 0. Since both inputs of the second gate are 0, Q will become 1.

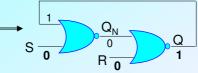

### S=0, R=0 / Q=1:

If we change S to 0, the latch will remain in the present state (1) because Q=1 feeds back into the first gate, causing  $Q_N$  to remain 0, as shown above.

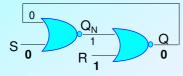

### S=0, R=1 / Q=0:

→

If we now change R to 1, Q will become 0 and  $Q_N$  will then change back to 1.

If we then change R back to 0, the latch remains in the present state (0).

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2023 Feza BUZLUCA

# Asynchronous "Clear" and "Preset" inputs

Clocked integrated circuit flip-flops often have additional inputs, which can be used to set the flip-flop to an initial state **independent of the clock** (asynchronous).

• PR (Preset) is used to write a "1" to the flip-flop.

A "1" applied to the preset (PR) input will set the flip-flop to Q = 1.

• CLR (Clear) is used to write a "0".

A "1" applied to the clear (CLR) input will reset the flip-flop to Q = 0.

These asynchronous inputs override the clock and D inputs.

That is, a "1" applied to the clear input will reset the flip-flop regardless of the values of D and the clock.

These asynchronous inputs can be used to assign initial values to the flip-flops after power-on reset.

Some devices use negative logic for PR and CLR inputs.

For example, in such a device, a "0" must be applied to the clear (CLR) input to reset the flip-flop to Q=0.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.33

# Digital Circuits

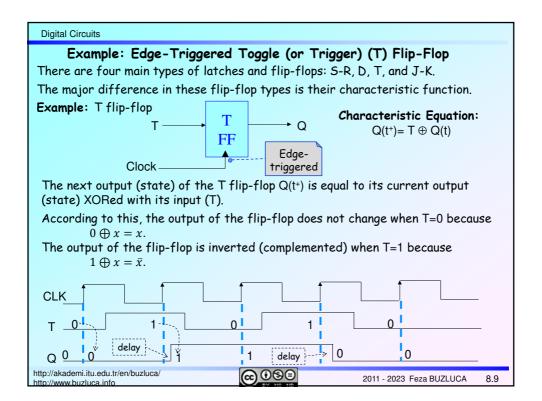

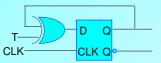

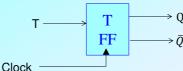

### Edge-Triggered Toggle (T) Flip-Flop

An edge-triggered T flip-flop can be implemented using an edge-triggered D flip-flop and an XOR gate.

If the input is 0 (T=0), the value of the flip-flop is preserved as  $0 \oplus Q = Q$ .  $T = 0 \rightarrow Q(t+1) = Q(t)$

If the input is 1 (T=1), the value of the flip-flop is complemented (toggled) because  $1 \oplus Q = \overline{Q}$ .

$T = 1 \rightarrow Q(t+1) = \overline{Q(t)}$

Characteristic Equation:  $Q(t+1) = T \oplus Q(t)$

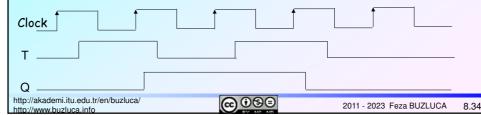

# Edge-Triggered J-K Flip-Flop

The J-K flip-flop combines the features of the S-R and T flip-flops.

- A "1" input applied to J or K alone acts exactly like an S or R input, respectively.

- if J = 1, K = 0, the latch output is set to Q = 1;

- if J = 0, K = 1, the latch output is reset to Q = 0.

- If a "1" input is applied to both simultaneously (J=1 and K=1), the flip-flop changes state (toggles) just like a T flip-flop.

### Digital Circuits

### Characteristic Equations of Latches and Flip-Flops:

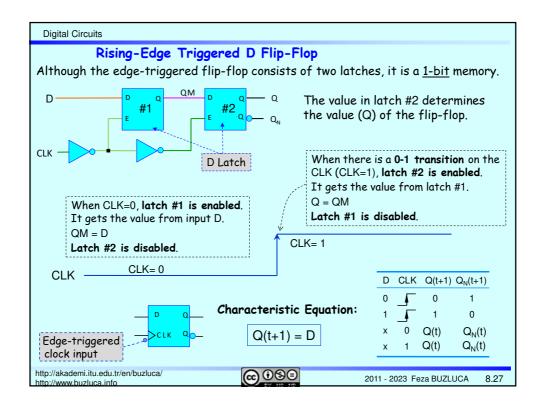

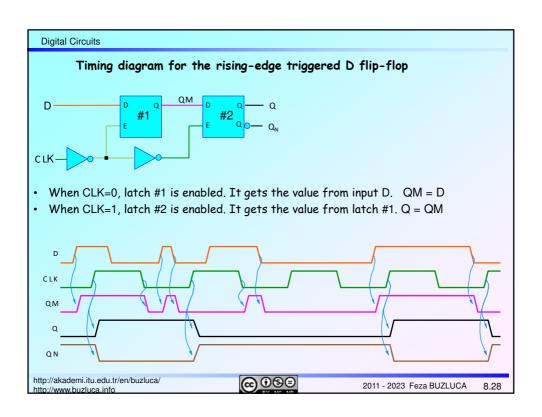

The functional behavior of a latch or flip-flop can be described by a **characteristic equation** that specifies the next state of the flip-flop (or latch) as a function of its inputs and current state.

# Characteristic equations of flip-flops:

S-R FF:  $Q(t+1) = S + \overline{R} \cdot Q(t)$  (SR = 0)

J-K FF :  $Q(t+1) = J \cdot \overline{Q(t)} + \overline{K} \cdot Q(t)$

D FF: Q(t+1) = D

T FF:  $Q(t+1) = T \oplus Q(t)$

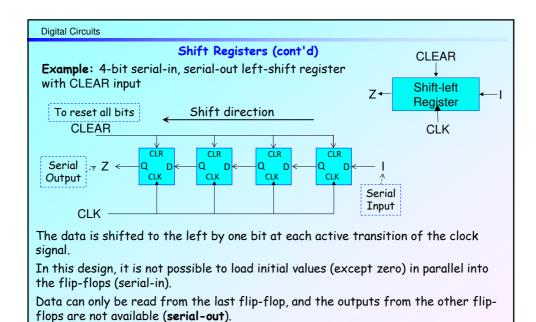

A right-shift register can be implemented by changing the order of the flip-flops.

**@ ⊕ ⊕**

2011 - 2023 Feza BUZLUCA

http://akademi.itu.edu.tr/en/buzluca/

http://www.buzluca.info

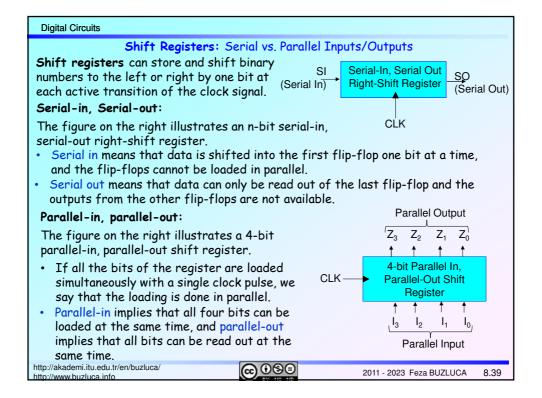

### Shift Register Configurations

Four register configurations (the combinations resulting from a choice of parallel or serial for the inputs and the outputs) are possible:

- · Parallel-in, Parallel-out

- · Serial-in, Serial-out

- Parallel-in, Serial-out

- Serial-in, Parallel-out

### Shift Register Applications

- Many computers operate on parallel data, but this data must sometimes be converted to serial format to be sent.

- Throughout most of the history of personal computers, data has been transferred through serial ports to devices such as modems, terminals, and various peripherals and directly between computers.

- ICs called UARTs (universal asynchronous receiver-transmitters) are used to interface microprocessors and parallel data to communications links that use serial data.

- Shift registers can perform this parallel-to-serial conversion and serial-toparallel conversion.

- Shift registers are available in IC form or can be constructed from discrete flip-flops.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

8.41

# Digital Circuits Example: 4-bit left-shift register with parallel load (inputs), serial output In this design, we can load an initial value to the register in parallel. SHIFT / LOAD = 0 : shift SHIFT / LOAD = 1 : load SHIFT / LOAD = 1 : load Serial Output Output

$I_3$

The shift register has the control input  $\overline{SHIFT}/LOAD$ , which enables either a shift or a load:

Parallel Inputs I<sub>3</sub>-I<sub>0</sub>

- If  $\overline{SHIFT}/LOAD = 0$ , clocking the register causes the serial input (I $_0$ ) to be shifted into the first flip-flop  $Q_0$ , while the data in flip-flops  $Q_3$ ,  $Q_2$ , and  $Q_1$  are shifted left

- If  $\overline{SHIFT}/LOAD = 1$ , clocking the shift register will cause the four data inputs ( $I_3$ ,  $I_2$ ,  $I_1$ , and  $I_0$ ) to be loaded in parallel into the flip-flops.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

**CLK**

Parallel/Serial Input

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

Example: 74164 8-Bit Serial-In Parallel-Out Shift Register

Serial data is entered through a 2-input AND gate (A and B) synchronous with the LOW-to-HIGH transition of the clock (CLK).

This register does not have parallel load capability ( $Q_7$ - $Q_0$  are outputs).

This device also has an asynchronous Master Reset (MR'), which clears the register by resetting all outputs to LOW independent of the clock.

For details, you may refer to the datasheet of the device.

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2023 Feza BUZLUCA