| Computer Architecture                                                                                                                                                                                       | Computer Architecture                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

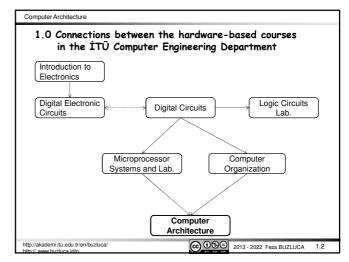

| 1.1. Why study Computer Architecture?                                                                                                                                                                       | 1.1. Why study Computer Architecture? (cont'd)<br>From: IEEE/ACM Computer Engineering Curricula 2016:                                                                                                    |

| From: Curriculum Guidelines for Undergraduate Degree Programs in Computer<br>Science (2013)                                                                                                                 | "One area of concern to the computer engineer is the software/hardware interface,<br>where difficult trade-off decisions often provide engineering challenges.                                           |

| prepared by the Joint Task Force on Computing Curricula<br>of the IEEE (Institute of Electrical and Electronics Engineers) Computer Society                                                                 | Considerations on this interface or boundary lead to an appreciation of and insights<br>into <b>computer architecture</b> and the importance of a computer's machine code.                               |

| and ACM (Association for Computing Machinery)                                                                                                                                                               | At this boundary, difficult decisions regarding hardware/software trade-offs can<br>occur, and they lead naturally to the design of special-purpose computers and systems.                               |

| <ul> <li><u>https://www.acm.org/education/curricula-recommendations</u></li> <li>Computing professionals should not regard the computer as just a black box<br/>that executes programs by magic.</li> </ul> | For example, in the design of a safety-critical system, it is important to ensure that the system not harm the user or the public.                                                                       |

| <ul> <li>Computer architecture is a key component of computer engineering, and the<br/>practicing computer engineer should have (at least) a practical understanding<br/>of this topic.</li> </ul>          | The computer engineer must thoroughly test, even with unlikely parameters, the<br>hardware and software, and ultimately the system itself, to ensure that the system<br>operates properly and reliably." |

| <ul> <li>Students need to understand computer architecture to develop programs<br/>that can achieve high performance through a programmer's awareness of<br/>parallelism and latency.</li> </ul>            | The Purpose of the Course 1. Learning how to provide hardware-based solutions (design computer systems) to engineering problems (considering speed, cost)                                                |

| <ul> <li>In selecting a system to use, students should be able to understand the<br/>tradeoff among various components, such as CPU clock speed, cycles per</li> </ul>                                      | <ol> <li>Learning how to choose an appropriate computer system to solve a problem<br/>(to realize a project) considering requirements such as processing and memory<br/>capabilities</li> </ol>          |

| instruction, memory size, and average memory access time.                                                                                                                                                   | 3. Developing high-quality software for large and embedded systems                                                                                                                                       |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                       | http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                    |

| Topics:                                                |                             |

|--------------------------------------------------------|-----------------------------|

| • The Pipeline                                         |                             |

| <ul> <li>Instruction Pipeline (Instruction)</li> </ul> | tion-Level Parallelism)     |

| <ul> <li>Pipeline hazards and solution</li> </ul>      | S                           |

| Input/Output Organization                              |                             |

| <ul> <li>Handshaking</li> </ul>                        |                             |

| $\cdot$ Data transfer between CPU                      | and memory                  |

| • Exceptions and Interrupts                            |                             |

| <ul> <li>Vectors, multiple interrupts,</li> </ul>      | priority, nested interrupts |

| Direct Memory Access - DMA                             |                             |

| • Memory Organization                                  |                             |

| <ul> <li>Cache memory</li> </ul>                       |                             |

| <ul> <li>Virtual Memory (Operating)</li> </ul>         | systems)                    |

| RAID: (Redundant Array of Inde                         | pendent/Inexpensive Disks)  |

| • Multiprocessor and multicore sys                     | items                       |

| <ul> <li>Cache coherence</li> </ul>                    |                             |

| Computer Architecture                                     | License: https://creativecommons.org/licenses/by-nc-nd/4.0/ | Computer Architecture                                                                                                                        |

|-----------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3 The Centra                                            | l Processing Unit - CPU                                     | 1.3.1.1 According to instruction sets and addressing modes:                                                                                  |

| 1.3.1 Categorization of C                                 | PLIe                                                        | a) CISC (Complex Instruction Set Computer)                                                                                                   |

| •                                                         |                                                             | b) RISC (Reduced Instruction Set Computer)                                                                                                   |

| CPUS can be categorized b                                 | ased on various properties:                                 | CISC:                                                                                                                                        |

| • Numbers of operands:                                    |                                                             |                                                                                                                                              |

|                                                           | ess machines (stack machines)                               | Motivation:                                                                                                                                  |

| •                                                         |                                                             | <ul> <li>A desire to simplify compilers. The machine language is made to look as much<br/>like a high-level language as possible.</li> </ul> |

|                                                           | ess machines (accumulator machines)                         | <ul> <li>A desire to improve performance. Shorter programs written with powerful</li> </ul>                                                  |

| <ul> <li>I wo operand/addre<br/>memory-memory)</li> </ul> | ess machines (register-register, register-memory,           | instructions                                                                                                                                 |

| , ,,                                                      | lange marking                                               | Characteristics;                                                                                                                             |

| <ul> <li>Three operand/add</li> </ul>                     |                                                             | <ul> <li>Large number of instructions (100-250)</li> </ul>                                                                                   |

| <ul> <li>Instruction sets and a</li> </ul>                | ddressing modes                                             | <ul> <li>Complex instructions and complex addressing modes (indirect memory acces)</li> </ul>                                                |

| <ul> <li>CISC (Complex Inst</li> </ul>                    | truction Set Computer)                                      | <ul> <li>Instructions that directly operate on memory locations</li> </ul>                                                                   |

| <ul> <li>RISC (Reduced Ins</li> </ul>                     | truction Set Computer)                                      | Microprogrammed control unit                                                                                                                 |

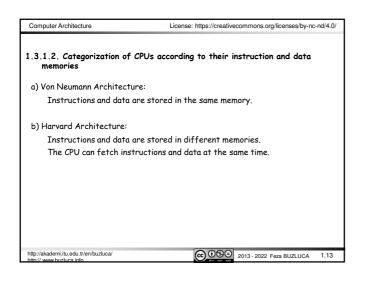

| <ul> <li>Instruction and data n</li> </ul>                | namoniae                                                    | Consequences:                                                                                                                                |

|                                                           |                                                             | <ul> <li>Instructions have different lengths (difficult to decode and prefetch).</li> </ul>                                                  |

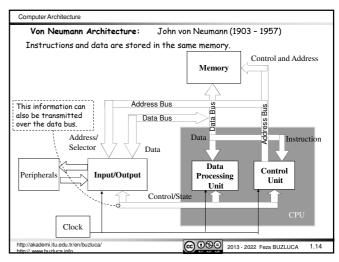

| <ul> <li>Von Neumann archi</li> </ul>                     |                                                             | <ul> <li>Some instructions are used very rarely.</li> </ul>                                                                                  |

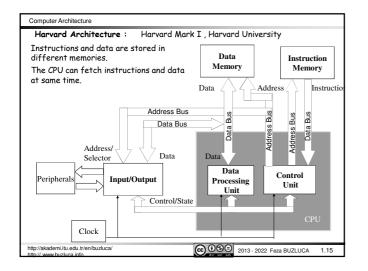

| <ul> <li>Harvard architectu</li> </ul>                    | ire                                                         | <ul> <li>The processor has a complex internal structure.</li> </ul>                                                                          |

| http://akademi.itu.edu.tr/en/buzluca/                     | 2013 - 2022 Feza BUZLUCA 1.7                                | http://akademi.itu.edu.tr/en/buzluca/                                                                                                        |

| Computer Architecture                                                                                                                                                                                       | Computer Architecture                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RISC:                                                                                                                                                                                                       | Characteristics of Reduced Instruction Set Architectures                                                                                                                                              |

| Motivation: Programs written in high-level languages were compiled on CISC processors, and analysis of the generated code yielded the following results.<br>• There are many assignment operations (A = B). | Although a variety of different approaches to reduced instruction set<br>architecture have been taken, certain characteristics are common to all of them:<br>• A small set of instructions (about 30) |

| <ul> <li>Most of the instructions in a compiled program are the relatively simple ones.</li> </ul>                                                                                                          | <ul> <li>Simple instructions with simple format (fixed length, easy to decode)</li> </ul>                                                                                                             |

| Complex machine instructions are often hard to exploit because the compiler                                                                                                                                 | <ul> <li>Simple addressing modes</li> </ul>                                                                                                                                                           |

| <ul> <li>must find those cases that exactly fit the construct.</li> <li>Accessed operands are mostly local and scalar (not array or vector).</li> </ul>                                                     | Register-to-register operations                                                                                                                                                                       |

| <ul> <li>Function calls (subroutines) have a large overhead: saving the return address,</li> </ul>                                                                                                          | <ul> <li>Memory access only for load/store instructions (load-store architecture).</li> </ul>                                                                                                         |

| transfer of parameters, local variables, stack (memory) access                                                                                                                                              | One instruction per clock cycle (owing to pipelining)                                                                                                                                                 |

| <ul> <li>Most (98%) of the subroutines transfer 6 or fewer parameters.<sup>1</sup></li> </ul>                                                                                                               | Hardwired control unit                                                                                                                                                                                |

| <ul> <li>Most (92%) of the subroutines use 6 or fewer local scalar variables.<sup>1</sup></li> </ul>                                                                                                        | Other Characteristics:                                                                                                                                                                                |

| <ul> <li>Depth of nesting function calls is mostly (99%) less than 8.<sup>2</sup></li> </ul>                                                                                                                | Not all of the features listed below are included in all RISC processors, and CISC                                                                                                                    |

| Based on these results, RISC processors with simple instructions which operate                                                                                                                              | processors may also include some of these features:                                                                                                                                                   |

| only on registers and access memory only for load/store operations were designed.                                                                                                                           | • A large number of registers (128-256) (Register File)                                                                                                                                               |

|                                                                                                                                                                                                             | Overlapped register window to transfer parameters and to save local data                                                                                                                              |

| <ol> <li>Andrew S. Tanenbaum, Implications of structured programming for machine architecture,<br/>Communications of the ACM, Vol.21, No.3 (1978), pp. 237 - 246</li> </ol>                                 | Instruction pipeline                                                                                                                                                                                  |

| 2. Yuval Tamir and Carlo H. Sequin, "Strategies for Managing the Register File in RISC,"                                                                                                                    | Harvard architecture                                                                                                                                                                                  |

| IEEE Transactions on Computers Vol. C-32(11) pp. 977-989, 1983.                                                                                                                                             | http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                 |

| http://akademi.itu.edu.tr/en/buziuca/ 2013 - 2022 Feza BUZLUCA 1.9                                                                                                                                          | http://akademi.itu.edu.tr/en/buziuca/<br>http://www.buziuca.info                                                                                                                                      |

| Computer Architecture                                                            |                                                         |

|----------------------------------------------------------------------------------|---------------------------------------------------------|

| Examples of CISC and RISC proce                                                  | ssors:                                                  |

| · CISC:                                                                          |                                                         |

| VAX, PDP-11, Intel x86 until P                                                   | entium, Motorola 68K.                                   |

| • RISC:                                                                          |                                                         |

| MIPS, SPARC, Alpha, HP-PA, F                                                     | PowerPC, i860, i960, ARM, Atmel AVR                     |

| <ul> <li>Hybrid (Outer CISC shell with an in<br/>Pentium, AMD Athlon.</li> </ul> | ner RISC core):                                         |

| There is a growing realization that                                              |                                                         |

| • RISC designs may benefit from the                                              | inclusion of some CISC features, and                    |

| • CISC designs may benefit from the                                              | inclusion of some RISC features.                        |

| The result is that                                                               |                                                         |

| <ul> <li>the more recent RISC designs, nota<br/>and</li> </ul>                   | bly the PowerPC, are no longer "pure" RISC              |

| • the more recent CISC designs, nota models, do incorporate some RISC c          | bly the Pentium II and later Pentium<br>haracteristics. |

| http://akademi.itu.edu.tr/en/buzluca/                                            | 2013 - 2022 Feza BUZLUCA 1.11                           |

| Computer Architecture |  |

|-----------------------|--|

|                       |  |

# Examples of products where RISC processors are used: • ARM:

- Apple iPod, Apple iPhone, iPod Touch, Apple iPad.

- Samsung mobile devices (Cortex-A)

RIM BlackBerry smartphone/email device

Microsoft Windows Mobile

- $\boldsymbol{\cdot}$  Nintendo Game Boy Advance

- · MIPS:

- SGI computers, PlayStation, PlayStation 2

• Power (Performance Optimization With Enhanced RISC) Architecture by IBM:

2013 - 2022 Feza BUZLUCA 1.12

- IBM supercomputers, midrange servers, and workstations

- Apple PowerPC-based Macintosh

- Nintendo Gamecube, Wii

- Microsoft Xbox 360

- Sony PlayStation 3

- Atmel AVR:

# • BMW cars

http://akademi.itu.edu.tr/en/buzluca/

### Computer Architecture

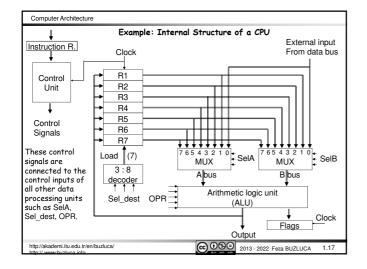

### 1.3.2 Internal Structure of a CPU

### Data Processing Unit:

- Performs data processing and internal data storage functions.

- Includes registers, arithmetic-logic unit, floating point unit, data pipeline.

# Control Unit:

- Decodes and interprets instructions; provides control signals to the data processing unit.

- Actually controls the operation of the CPU and hence the computer.

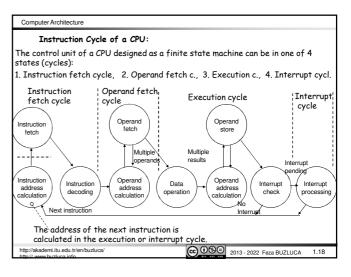

- Is designed as a finite state machine (refer to instruction cycles of the CPU for the states (instruction fetch, data fetch, execution, etc.))

- Can be implemented as a

- synchronous sequential circuit (hardwired) or

- microprogrammed machine.

Remember each instruction in the machine language of the processor is translated into a sequence of lower-level control unit instructions which are called microinstructions.

The internal structure of an exemplary CPU is shown on slide 1.17. http://dadami.iu.edu.tr/anbuzuca/ http://dadami.iu.e

| Computer Architecture                                                                                                                                                                                                                                                         | Computer Architecture                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>4 CPU Performance and Its Factors<br/>Remember: All synchronous sequential digital circuits are constructed using a clock         signal running at a constant rate (See BLG 231E lecture notes).</li> </ol>                                                         | <b>1.4.2 Clock cycles per instruction (CPI):</b><br>The average number of clock cycles each instruction takes to execute.                                                                                                             |

| These discrete time events are called clock periods, clocks, cycles, or clock cycles.<br>We refer to the time of a clock period by its duration (e.g., 0.5 ns) or by its rate<br>(e.g., 2 GHz).<br>Remember: Since the CPU is implemented as a synchronous sequential digital | $CPI = \frac{CPU \ clock \ cycles \ for \ a \ program}{Instruction \ count} \ (IC)$ Here, instruction count (IC) is the number of machine-language instructions that constitute the program.                                          |

| circuit, it is also triggered by a clock signal.<br>1.4.1 CPU execution time for a program:                                                                                                                                                                                   | These instructions are either generated by the compilers from high-level programs or written by the systems programmers using the assembly language of the processor.                                                                 |

| CPU Time = CPU clock cycles for a program X Clock cycle time<br>or $CPU Time = \frac{CPU clock cycles for a program}{Clock rate}$ $Clock rate = \frac{1}{Clock cycle}$                                                                                                        | Since different instructions may take different amounts of time depending on what they do (especially in CISC processors), CPI is <b>an average</b> of all the instructions executed in the program.<br>Example: MC68000 instructions |

| The hardware designer can improve performance by reducing the number of clock<br>cycles required for a program or the length of the clock cycle.                                                                                                                              | CLR.W D0;       Clear Data register D0       8 cycles         ADD.W (A1)+,D0;       Add data pointed by A1 to D0 and increment A1       16 cycles                                                                                     |

| However, there is often a trade-off between the number of clock cycles needed for a program and the length of each cycle. Many techniques that decrease the number of clock cycles may also increase the clock cycle time.                                                    | Each execution of a given instruction may take a different number of clock cycles due to data and branch hazards (pipelining, DMA; we will discuss these topics later).                                                               |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                                                                                         | http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                                                 |

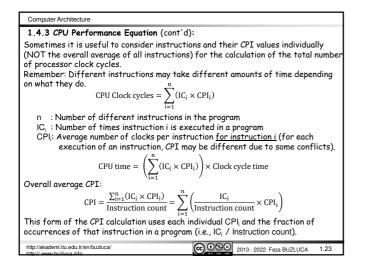

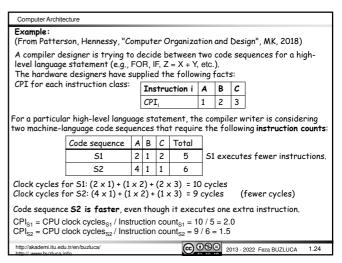

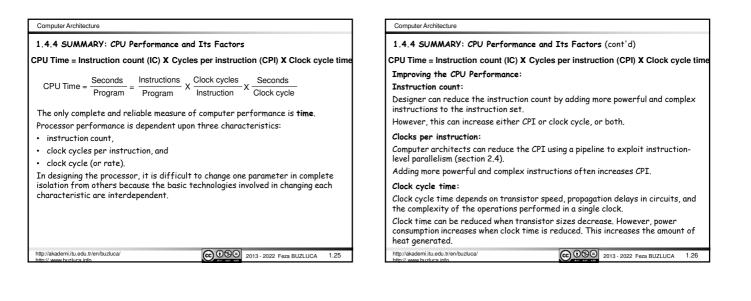

| CPU Time = instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time<br>or, since the clock rate is the inverse of clock cycle time:<br>CPU Time = $\frac{\text{Instruction count (IC) X Cycles per instruction (CPI)}}{\text{CPU Time} = \frac{\text{CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock}{\text{CPU time}_A = CPU clock cycles}_A X Clock cycle time}{\text{CPU time}_A = CPU clock}{\text{CPU time}_A $ | Computer Architecture                                                                       | Computer Architecture                                                                                                    |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Required clock cycles for a program:       Two implementations of the same instruction set architecture.         CPU Clock Cycles = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time: 250 ps (0.25 ns) and a CPI of 2.0 for some program.         CPU Time = CPU Clock Cycles X Clock cycle time       Clock cycle time: 500 ps (0.5 ns) and a CPI of 1.2 for the same program and by how much?         Basic performance equation:       CPU Time = IC X CPI X Clock cycles time         CPU Time = IC X CPI X Clock cycles per instruction (CPI) X Clock cycle time:       Which computer is faster for this program and by how much?         Solution:       Each computer executes the same number of instructions (IC) for CPU clock cycles are instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycles are CPU clock cycles are counter executes the same number of instructions (IC) for CPU clock cycles are CPU clock cycles be instructions (IC) for CPU clock cycles be instructions (IC) for CPU time are CPU clock cycles be instructions (IC) for CPU time are CPU clock cycles be set to computer are counter are cycles and the program and by how much?         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = CPU clock cycle time:       CPU time are CPU clock cycles be set to conce cycle time.         CPU time = CPU clock cycle time:       Computer are cycles be cycle time.         CPU time = CPU clock cycles be                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.4.3 CPU Performance Equation:                                                             | Example:                                                                                                                 |  |  |  |  |  |

| CPU Clock Cycles = Instruction count (IC) X Cycles per instruction (CPI)         CPU time for the program:         CPU Time = CPU Clock Cycles X Clock cycle time         Basic performance equation:         CPU Time = IC X CPI X Clock cycle time         CPU Time = IC X CPI X Clock cycle time         CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = CPU clock cycles A Clock cycle time:         CPU Time = CPU clock cycles a feeting performance characteristics:         • Clock cycle time: Hardware technology and organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             | Two implementations of the same instruction set architecture.                                                            |  |  |  |  |  |

| CPU time for the program:       Computer for the program:         CPU Time = CPU Clock Cycles X Clock cycle time       Computer B:         Basic performance equation:       Clock cycle time: 500 ps (0.5 ns) and a CPI of 1.2 for the same p         CPU Time = IC X CPI X Clock cycle time       Solution:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:       Solution:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = CPU Clock cycles per instruction (CPI)       Clock cycles per instruction (CPI)         CPU Time = CPU Clock cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU time <sub>A</sub> = CPU clock cycles X Clock cycle time <sub>A</sub> CPU time <sub>A</sub> = CPU clock cycles X Clock cycle time <sub>A</sub> CPU time <sub>B</sub> = CPU clock cycles be = 500 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             | Computer A: picoseconds                                                                                                  |  |  |  |  |  |

| CPU Time = CPU Clock Cycles X Clock cycle time       Clock cycles time: 500 ps (0.5 ns) and a CPI of 1.2 for the same p         Basic performance equation:       Clock cycle time: 500 ps (0.5 ns) and a CPI of 1.2 for the same p         CPU Time = IC X CPI X Clock cycle time       Which computer is faster for this program and by how much?         Solution:       Each computer executes the same number of instructions (IC) for CPU clock cycles <sub>A</sub> = IC X 2.0         or, since the clock rate is the inverse of clock cycle time:       CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycle time:         CPU Time = CPU Clock cycles a flecting performance characteristics:       Clock cycle time: Hardware technology and organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |                                                                                                                          |  |  |  |  |  |

| Basic performance equation:       Which computer is faster for this program and by how much?         CPU Time = IC X CPI X Clock cycle time       Solution:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:       Each computer is faster for this program and by how much?         or, since the clock rate is the inverse of clock cycle time:       CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock cycles per instruction (CPI)         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles per instruction (CPI)       Clock rate         CPU time = CPU clock cycles per instruction (CPI)       Clock rate         CPU time = CPU clock cycles per instruction (CPI)       Clock rate         CPU time = CPU clock cycles per instruction (CPI)       Clock cycles per instruction count (IC) to cycles per instruction (CPI)         Clock cycle time:       Clock cycles per instruction (CPI) <t< td=""><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                             |                                                                                                                          |  |  |  |  |  |

| Basic performance equation:       Solution:         CPU Time = IC X CPI X Clock cycle time       Solution:         CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:       Each computer executes the same number of instructions (IC) for CPU clock cycles <sub>A</sub> = IC X 2.0         or, since the clock rate is the inverse of clock cycle time:       CPU Time = Instruction count (IC) X Cycles per instruction (CPI)         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles <sub>A</sub> X Clock cycle time <sub>A</sub> CPU time <sub>A</sub> = CPU clock cycles <sub>B</sub> X Clock cycle time <sub>A</sub> CPU Time = CPU time = CPU clock cycles <sub>B</sub> X Clock cycle time <sub>B</sub> Computer         CPU time <sub>B</sub> = CPU clock cycles <sub>B</sub> X Clock cycle time <sub>B</sub> Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 500 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 500 X IC ps       Computer         CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 500 X IC ps       Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CFU Time = CFU Clock Cycles & Clock Cycle time                                              |                                                                                                                          |  |  |  |  |  |

| CPU Time = ICX CP1 X Clock cycle time         CPU Time = Instruction count (IC) X Cycles per instruction (CP1) X Clock cycle time:         or, since the clock rate is the inverse of clock cycle time:         CPU Time = Instruction count (IC) X Cycles per instruction (CP1)         CPU Time = Instruction count (IC) X Cycles per instruction (CP1)         CPU Time = Instruction count (IC) X Cycles per instruction (CP1)         CPU Time = CPU clock cycles A Clock cycle time.         CPU Time = CPU time = CPU clock cycles A Clock cycle time.         CPU Time = CPU time = CPU clock cycles A Clock cycle time.         CPU time = CPU clock cycles A Clock cycle time.         CPU time = CPU clock cycles A Clock cycle time.         CPU time = CPU clock cycles A Clock cycle time.         CPU time = CPU clock cycles B CO X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps         CPU time = IC X 1.2 X 500 ps = 600 X IC ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Basic performance equation:                                                                 |                                                                                                                          |  |  |  |  |  |

| CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time:       CPU clock cycles_a = IC X 2.0         or, since the clock rate is the inverse of clock cycle time:       CPU clock cycles_a = IC X 1.2         CPU Time = Instruction count (IC) X Cycles per instruction (CPI)       Clock rate         CPU Time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time_a         CPU Time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time_a         CPU time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time_a         CPU time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time_a         CPU time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time_a         CPU time = CPU clock cycles_a X Clock cycle time;       CPU time_a = CPU clock cycles_a X Clock cycle time;         CPU time = IC X 1.2 X 500 ps = 600 X IC ps       Compute         CPU time = IC X 1.2 X 500 ps = 600 X IC ps       Compute         CPU time;       If amount faster is given by the ratio of the execution times:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CPU Time = IC X CPI X Clock cycle time                                                      |                                                                                                                          |  |  |  |  |  |

| CPU Time =       Instruction count (IC) X Cycles per instruction (CPI)         CPU Time =       CPU time =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CPU Time = Instruction count (IC) X Cycles per instruction (CPI) X Clock cycle time         | Each computer executes the same number of instructions (IC) for the program.<br>CPU clock cycles <sub>A</sub> = IC X 2.0 |  |  |  |  |  |

| CPU Time =       CPU time A = IC X 2.0 X 250 ps = 500 X IC ps         CPU time a = IC X 2.0 X 250 ps = 500 X IC ps       Compute         CPU time b = CPU clock cycles X Clock cycles time b = CPU time b =                                                                                                                                                                                                                                                                                                                                              | or, since the clock rate is the inverse of clock cycle time:                                | CPU clock cycles <sub>B</sub> = IC X 1.2                                                                                 |  |  |  |  |  |

| Clock rate       Clock rate         Technologies affecting performance characteristics:       CPU time <sub>B</sub> = CPU clock cycles <sub>B</sub> X Clock cycle time <sub>B</sub> Clock cycle time: Hardware technology and organization       The amount faster is given by the ratio of the execution times:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Instruction count (IC) X Cycles per instruction (CPI)                                       |                                                                                                                          |  |  |  |  |  |

| Technologies affecting performance characteristics:       CPU time <sub>B</sub> = IC X 1.2 X 500 ps = 600 X IC ps         • Clock cycle time: Hardware technology and organization       The amount faster is given by the ratio of the execution times:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             | CPU time <sub>A</sub> = IC X 2.0 X 250 ps = <b>500 X IC ps</b>                                                           |  |  |  |  |  |

| Clock cycle time: Hardware technology and organization     The amount faster is given by the ratio of the execution times:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             | CPU time <sub>B</sub> = CPU clock cycles <sub>B</sub> X Clock cycle time <sub>B</sub> Computer A is faster.              |  |  |  |  |  |

| older cycle mile hardware reenhology and organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Technologies affecting performance characteristics:                                         |                                                                                                                          |  |  |  |  |  |

| CPI: Organization and instruction set architecture     Instruction count: Instruction set architecture and compiler technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>Clock cycle time: Hardware technology and organization</li> </ul>                  | 5,                                                                                                                       |  |  |  |  |  |

| • Instruction count: Instruction set architecture and compiler technology CPU performance <sub>B</sub> = 1 / Execution time <sub>B</sub> = Execution time <sub>A</sub> = 500 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>CPI: Organization and instruction set architecture</li> </ul>                      | CPU performance <sub>A</sub> 1 / Execution time <sub>A</sub> Execution time <sub>B</sub> 600 X IC ps                     |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Instruction count: Instruction set architecture and compiler technology</li> </ul> | CPU performance <sub>B</sub> $=$ 1 / Execution time <sub>B</sub> $=$ Execution time <sub>A</sub> $=$ 500 X IC ps $=$ 1.2 |  |  |  |  |  |

| http://akademi.itu.edu.tr/en/buzluca/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | http://akademi.itu.edu.tr/en/buzluca/                                                       | http://akademi.itu.edu.tr/en/buzluca/                                                                                    |  |  |  |  |  |

# Computer Architecture License: https://creativecommons.org/licenses/by-nc-nd/4.0/

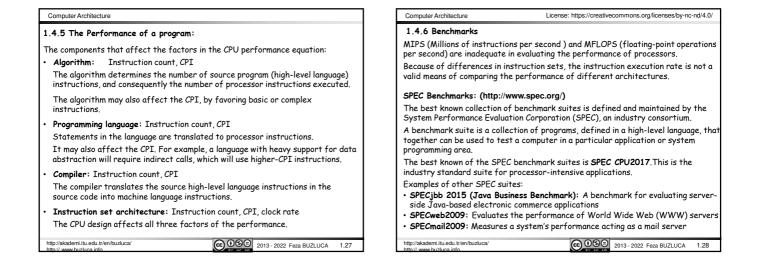

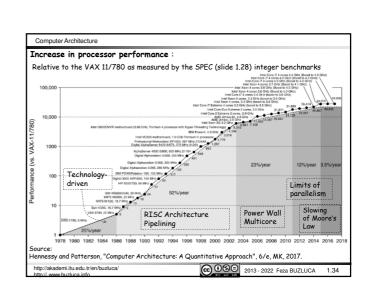

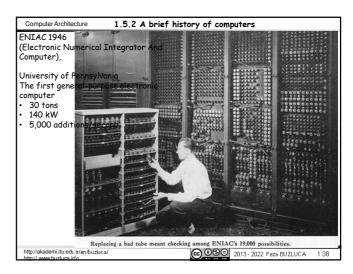

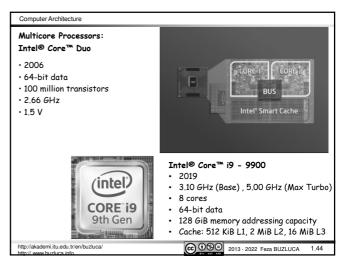

### 1.5 The evolution of computers

## Characteristics of evolution:

Increase in processor speed, increase in level of integration of circuits, decrease in component size, increase in memory size, and increase in I/O capacity and speed. Reasons for the increase in processor speed:

### Achievemente in processor sp

Achievements in material:

Shrinking size of microprocessor components (this reduces the distance between components and hence increases speed)

# Organizational improvements:

Heavy use of pipelining and parallel execution techniques, multiple ALUs multicore designs

Cache memories

In this course, we will discuss the organizational improvements.

http://akademi.itu.edu.tr/en/buzluca/

2013 - 2022 Feza BUZLUCA 1.29

# Computer Architecture

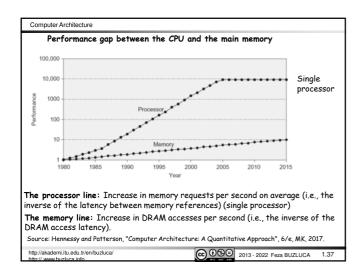

1.5.1 Improvements and Problems in Computer Organization and Architecture There are three main approaches to achieving increased processor speed: 1. Increasing the hardware speed of the processor (clock speed) (But !) 2. Making changes to the processor organization and architecture that increase the effective speed of instruction execution (parallelism, pipeline) 3. Increasing the size and speed of cache memories As clock speed and logic density increase, a number of problems arises (#1 above). **Power:** It is difficult to dissipate the heat generated on high-density, high-speed chips (the power wall, slide 1.31). RC delay: The speed at which electrons can flow on a chip between transistors is limited by the resistance and capacitance of the metal wires connecting them. The wire interconnects become thinner, increasing resistance. Also, the wires are closer together, increasing capacitance. Therefore, it is not possible to increase the clock speed. Memory latency: In addition, the speed of memories does not increase at the same rate as that of processors. Memory speeds lag processor speeds. http://akademi.itu.edu.tr/en/buzluca/ 2013 - 2022 Feza BUZLUCA 1.30

### Computer Architecture Computer Architecture Integration of circuits The Power Wall \* Moore's law (by Gordon Moore, cofounder of Intel): "The number of transistors Dynamic power per transistor (P) is proportional to frequency of operation (f) that can be put on a single chip is doubling every year and this pace will continue times the square of the operating voltage (V) $(P \sim V^2 f)$ into the near future". (1965) To reduce the power increase, the operating voltage can be decreased, but it is Since the 1970s, the number of transistors on integrated circuits has been limited by the transistors' operating threshold voltages. doubling approximately every 18 months. The total dynamic power dissipated by an entire IC can be expressed as $\mathbf{P} \sim \mathbf{N} \mathbf{f}$ , Today, most visible with DRAM capacity. Its growth is slowing down. where N represents the total number of transistors operating simultaneously. Gordon Moore expects Moore's law will end by around 2025. Increasing the number of transistors at Moore's law pace and increasing the Growth in Transistor Count on Integrated Circuits (DRAM): operating frequency is bound to reach a thermal dissipation limit—the power wall. By 2003, processors exceeded 200 W per chip. This milestone marked the transistor ICs Moore's law promulgated Firs 100 bn crossing of a power threshold that requires far more expensive cooling technologies, which were outside the system-cost envelope of PC hardware at 10 bn 1 bn chip 100 m 10 m that time. Transistors per The industry had to choose which to slow down: the growth of the 100,00 10,000 microprocessor's transistor number from one generation to the next, or the operational frequency rate. 1,000 100 They decided on the second option, which maintained Moore's law but sacrificed 10 frequency growth. 1947 55 75 80 95 2000 70 90 85 60 William Stallings, Computer Organization and Architecture, 10/e, Prentice Hall, 2016

\*Source: T. M. Conte, E. P. DeBenedictis, P. A. Gargini, and E. Track, "Rebooting Computing: The Road Ahead," Computer, vol. 50, no. 1, pp. 20-29, Jan. 2017. http://kadamii.lu.edu.fr/en/buzluca/ http://kadamii.lu.edu.fr/en/buzluca/ http://kadamii.lu.edu.fr/en/buzluca/ 2013 - 2022 Feza BUZLUCA 1.31

2013 - 2022 Feza BUZLUCA

1.32