| Computer Architecture                                |                              |  |  |  |

|------------------------------------------------------|------------------------------|--|--|--|

| Programmable Registers (User Programmer's Model)     |                              |  |  |  |

| Data Registers:                                      |                              |  |  |  |

| <ul> <li>consist of 8 identical registers</li> </ul> |                              |  |  |  |

| • can be addressed as 8                              | , 16, or 32 bits             |  |  |  |

|                                                      |                              |  |  |  |

|                                                      |                              |  |  |  |

| 31                                                   | <u> </u>                     |  |  |  |

|                                                      | D0                           |  |  |  |

|                                                      | D1                           |  |  |  |

|                                                      | D2                           |  |  |  |

|                                                      | D0                           |  |  |  |

|                                                      | D4                           |  |  |  |

|                                                      | D3                           |  |  |  |

|                                                      | D7                           |  |  |  |

|                                                      |                              |  |  |  |

|                                                      |                              |  |  |  |

|                                                      |                              |  |  |  |

| www.akademi.itu.edu.tr/buzluca                       | © 2005-2022 Feza BUZLUCA A.2 |  |  |  |

| www.buzluca.info                                     | © 2005-2022 Feza BUZLUCA A.2 |  |  |  |

Computer Architecture Address Registers: • 8+1 registers (A0 to A7 and A7'). These are typically used as pointers. • The address registers can only be used as 16 or 32 bits. • The A7 register is also the stack pointer. It is duplicated for the user and supervisor states, i.e, A7 (User Stack Pointer -USP) and A7' (System Stack Pointer -SSP). 31 16 15 0 A0 A1 A2 A3 A4 A5 A6 A7 (USP) A7' (SSP) Since the address bus is 24 bits wide, only the first 24 bits of the data in an address register is used. When the low-order word (16 bits) in an address register is used, these bits are sign-extended to 24 bits before being placed on the address bus. www.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.3

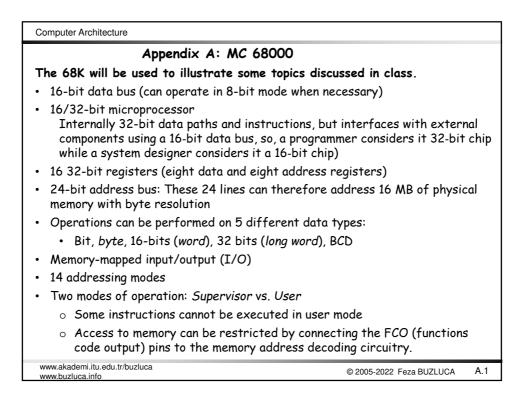

| Computer Architecture                                                                                                                                                                                                                                            |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Addressing Modes                                                                                                                                                                                                                                                 |  |  |  |

| <ul> <li>The 68000 supports 14 different addressing modes derived from six basic types:</li> <li>1. Register Direct</li> <li>2. Immediate</li> <li>3. Absolute</li> <li>4. Register Indirect</li> <li>5. Program Counter Relative</li> <li>6. Implied</li> </ul> |  |  |  |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                             |  |  |  |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                            |  |  |  |

| www.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.6 www.buzluca.info                                                                                                                                                                                     |  |  |  |

| Computer Architecture                                                                                                                                                                                                                                           |    |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 2a. Immediate                                                                                                                                                                                                                                                   |    |  |  |  |

| The actual data to be used as the operand is included in the instruction itself                                                                                                                                                                                 | f. |  |  |  |

| MOVE.L #\$4A7F0000, D0 ; move the immediate data \$4A7F0000 to D0                                                                                                                                                                                               | )  |  |  |  |

| 2b. Quick Immediate                                                                                                                                                                                                                                             |    |  |  |  |

| Can only be used with some instructions.                                                                                                                                                                                                                        |    |  |  |  |

| The source operand must use immediate mode, and only with an 8-bit signed integer constant (-128,, 127). The destination must be a D register.                                                                                                                  |    |  |  |  |

| The instruction takes up less space (2 bytes, not 6) and works faster.                                                                                                                                                                                          |    |  |  |  |

| For example, it is used for the MOVE instruction on 8-bit data.                                                                                                                                                                                                 |    |  |  |  |

| MOVEQ #5, D0 ; 32 bits of D0 are affected by this instruction                                                                                                                                                                                                   | n  |  |  |  |

| 3a. Absolute Short<br>The instruction provides the 16-bit address of the operand in memory. The<br>16-bit address is sign-extended to 24 bits.                                                                                                                  |    |  |  |  |

| MOVE.B D0, (\$58AA) ; written to address \$0058AA                                                                                                                                                                                                               |    |  |  |  |

| MOVE.B D0, (\$B51A) ; written to address \$FFB51A                                                                                                                                                                                                               |    |  |  |  |

| <ul> <li>3b. Absolute Long         Used when the address size is more than 16 bits.         The instruction provides the 24-bit address of the operand in memory.         MOVE.W (\$45C720),D7 ; 16 bits starting at location \$45C720 written to D7</li> </ul> |    |  |  |  |

| www.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.7<br>www.buzluca.info                                                                                                                                                                                 |    |  |  |  |

| Computer              | Architecture                | Э       |                                                |         |                                        |        |                                       |

|-----------------------|-----------------------------|---------|------------------------------------------------|---------|----------------------------------------|--------|---------------------------------------|

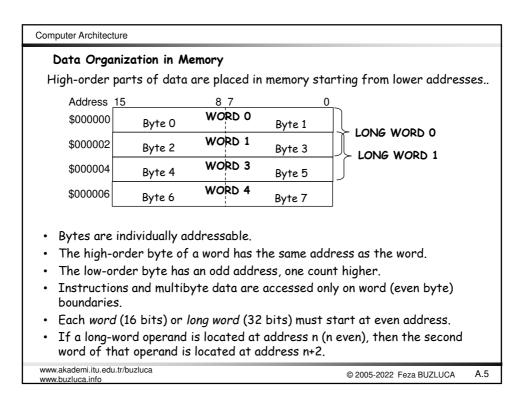

| 4. Register Indirect  |                             |         |                                                |         |                                        |        |                                       |

| 4a. Ada               | dress Re                    | giste   | r Indirect                                     |         |                                        |        |                                       |

| And                   | address r                   | regis   | ter contains the ad                            | dress o | f the source or de                     | sti    | nation operand.                       |

|                       | [                           | 31      | $A_n \longrightarrow$                          | data    | a                                      |        |                                       |

|                       | a <b>mple:</b><br>the exect | ution   | of the                                         |         | er the instruction<br>state of memory: | has    | · · · · · · · · · · · · · · · · · · · |

|                       | 31                          | 0       |                                                |         | MOVE.B D0, (A0)                        | _      | Memory<br>00100 C8 XX                 |

| Regi                  | sters                       |         | Content of D0 writ                             | ten to  |                                        |        | 00102 XX XX                           |

| D0                    | 4350 A                      |         | the address A0 poin                            | nts to. |                                        | ſ      | Memory                                |

| A0                    | 0000 10                     | 000     |                                                | ľ       | 40VE.W D0, (A0)                        | $\neg$ | 00100 A7C8                            |

| Mem                   | ory                         |         | content of AO does r                           | -       | •                                      |        | 00102 XX XX                           |

| 0010                  | 0 XX XX                     |         | h-order parts of data<br>rting from lower addr |         | ced in memory                          | Γ      | Memory                                |

| 0010                  | 2 XX XX                     |         |                                                | I       | MOVE.L D0, (A0)                        | $\neg$ | 00100 4350                            |

| 0010                  | 4 XX XX                     |         |                                                |         |                                        |        | 00102 A7C8                            |

| www.akad<br>www.buzlu | emi.itu.edu.tr/<br>uca.info | buzluca | L                                              |         | © 2005-2022                            | Feza   | BUZLUCA A.8                           |

| Computer Architecture                                                                                                                                           |                 |                                                                                                                                |                                                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|

| Inst                                                                                                                                                            | ruction Form    | at in MC68000                                                                                                                  | 15 0                                                                   |  |

| All instructions will be m                                                                                                                                      | Op word         |                                                                                                                                |                                                                        |  |

| Each instruction is at least 1 word, at most 5 words.<br>The instruction code (or op word) specifies the<br>instruction's operation and addressing modes of the |                 |                                                                                                                                | Immediate data (if any,<br>one or two words)<br>Source addr. extension |  |

| operands.                                                                                                                                                       |                 |                                                                                                                                | Dest. addr. extension                                                  |  |

| Instruction Format Examples:<br>Single Operand Instruction Format:                                                                                              |                 |                                                                                                                                |                                                                        |  |

| Instruction word:                                                                                                                                               | 15              | 3         7         6         5         4         3         2         1         0           Size         Mode         Register |                                                                        |  |

|                                                                                                                                                                 |                 | 01. W                                                                                                                          | the reference manual<br>odes in the Mode and<br>fields.                |  |

| E×ample:                                                                                                                                                        |                 |                                                                                                                                |                                                                        |  |

| CLR.W D3 0100                                                                                                                                                   | 0010 01 000 011 |                                                                                                                                |                                                                        |  |

|                                                                                                                                                                 | CLR W D 3       |                                                                                                                                |                                                                        |  |

| www.akademi.itu.edu.tr/buzluca<br>www.buzluca.info                                                                                                              |                 | © 200                                                                                                                          | 5-2022 Feza BUZLUCA A.13                                               |  |

| Computer Architecture                            |                                          |                                                            |

|--------------------------------------------------|------------------------------------------|------------------------------------------------------------|

| Examples continued                               | 1:                                       |                                                            |

| CLR.L (A2)+                                      | 01000010 10 011 010<br>CLR L (An)+ 2     | Address register indirect<br>postincrement                 |

| CLR.B (\$3000)                                   | 01000010 00 111 000<br>CLR B Absolute sh | Absolute addressing (short)                                |

|                                                  | 0011 0000 0000 0000                      | The address (\$3000) is in the second word.                |

| CLR.B \$4(A6)                                    | 01000010 00 101 110<br>CLR B d(An) 6     | Address register indirect with offset                      |

|                                                  | 0000 0000 0000 0100                      | The offset (\$4) is in the second word<br>as 16 bits.      |

| CLR.B -7(A6)                                     | 01000010 00 101 110<br>CLR B d(An) 6     | Address register indirect with offset<br>(negative offset) |

|                                                  | 1111 1111 1001                           | The offset (-7) is in the second word as 16 bits.          |

| www.akademi.itu.edu.tr/buzlu<br>www.buzluca.info | ica                                      | © 2005-2022 Feza BUZLUCA A.14                              |

| Computer Architecture                                                                                                                                                                                                                                        |                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Additional Word for Register Indirect with Index of                                                                                                                                                                                                          | and Offset Addressing Mode:                                                                                               |

| In the register indirect with index and offset addr additional word.                                                                                                                                                                                         | essing mode, there is an                                                                                                  |

| The additional word contains information about the                                                                                                                                                                                                           | index register and offset.                                                                                                |

| 15       14       13       12       11       10       9       8       7       0         D/A       Index reg       W/L       0       0       offset       0         0:D       0:W       8       bits reserved for offset       1:A       1:L         Example: |                                                                                                                           |

| CLR.W \$C2(A3, D7.L) 01000010 01 110 011<br>0 111 1 000 11000010<br>D 7 L \$C2                                                                                                                                                                               | CLR.W d(A3,Rn.S)<br>The additional word contains<br>information about the index<br>register and offset<br>(displacement). |

| www.akademi.itu.edu.tr/buzluca<br>www.buzluca.info                                                                                                                                                                                                           | © 2005-2022 Feza BUZLUCA A.15                                                                                             |

| Computer Architecture                                                                                                               |                                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| Instruction Format Examples (continued)                                                                                             |                                   |  |  |  |

| Two-Operand Instruction Format:                                                                                                     |                                   |  |  |  |

| Example: MOVE<br>15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0<br>0 0 Size Reg. Mod. Mod. Reg<br>01: B<br>11: W source destination<br>10: L |                                   |  |  |  |

| The instruction is not decoded based on just this field; the whole opword is used.                                                  |                                   |  |  |  |

| Example:                                                                                                                            |                                   |  |  |  |

| MOVE.W D2, (A5)+ 00 11 101 011 000 010                                                                                              |                                   |  |  |  |

| W 5 (An)+ D 2                                                                                                                       |                                   |  |  |  |

| Example:<br>MOVE.W #\$1234 , \$25(A3) 00 11 011 101 111 100                                                                         |                                   |  |  |  |

| 0001 0010 0011 0100                                                                                                                 | \$1234 (immediate data)           |  |  |  |

| 0000 0000 0010 0101                                                                                                                 | \$0025 (source address extension) |  |  |  |

|                                                                                                                                     |                                   |  |  |  |

| www.akademi.itu.edu.tr/buzluca<br>www.buzluca.info                                                                                  | © 2005-2022 Feza BUZLUCA A.16     |  |  |  |

| Computer Architecture                                                        |                                                                                                                                                       |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Quick Instruction Format:1511 10 9 8 70MOVEQ0111Reg.0data                    | <ul> <li>8-bit immediate data used.</li> <li>Source is a data register.</li> <li>32 bits of the register are affected by this instruction.</li> </ul> |

| Example:<br>MOVEQ #-5 , D2 0111 010 0 11111011<br>-5                         | <ul> <li>Takes up less space than<br/>normal immediate addressing.</li> </ul>                                                                         |

| The normal MOVE instruction that performs th words (48 bits) of space.       | e same operation takes up 3                                                                                                                           |

| MOVE.L #-5 , D2 L 2 D immediate<br>00 10 010 000 111 100<br>1111 1111 1111 1 | 32-bit "-5"                                                                                                                                           |

| ADDQ operates on 3-bit immediate data.                                       |                                                                                                                                                       |

| www.akademi.itu.edu.tr/buzluca<br>www.buzluca.info                           | © 2005-2022 Feza BUZLUCA A.17                                                                                                                         |

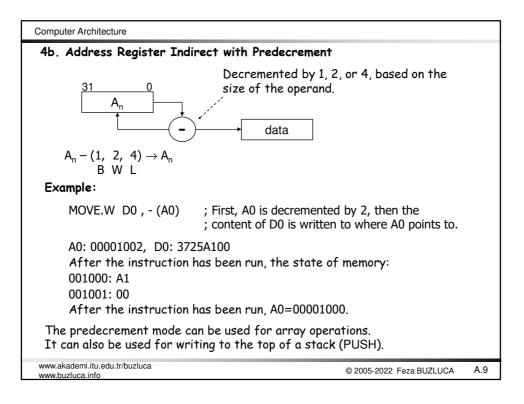

| Computer Architecture                                                                                                |                                                                                                                                                                        |                           |                          |                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------|

| MC68000 Instructions<br>In this section, we will introduce some MC68000 instructions.<br>Data Movement Instructions: |                                                                                                                                                                        |                           |                          |                                                                                                                      |

| MOVEM                                                                                                                | Move                                                                                                                                                                   | multiple re               | gisters                  |                                                                                                                      |

| data from<br>Syntax 1:                                                                                               | specified n<br>MOVEM <re< th=""><th></th><th>ess and pla<br/><ea></ea></th><th>arting at a specific address, or reads<br/>aces them in specified registers.</th></re<> |                           | ess and pla<br><ea></ea> | arting at a specific address, or reads<br>aces them in specified registers.                                          |

| Examples:                                                                                                            | MOVEM.L<br>MOVEM.L                                                                                                                                                     | D0-D7/A0-,<br>(A5) , D0/[ |                          | ; save D0-D7/A0-A6 to<br>; memory starting at \$1234<br>; read D0, D5, A0-A3,<br>; from memory address pointed by A5 |

| Can be used to save working registers on entry to a subroutine and to restore them at the end of a subroutine.       |                                                                                                                                                                        |                           |                          |                                                                                                                      |

|                                                                                                                      | L D0-D5/A0-<br><br>y of subrouti                                                                                                                                       | ·A3,-(A7)<br>ne           | ; Push re                | egisters D0-D5/A0-A3 onto the stack                                                                                  |

| MOVEM.<br>RTS                                                                                                        | <br>L (A7)+,D0-                                                                                                                                                        | D5/A0-A3                  |                          | e registers D0-D5/A0-A3 from the stack to the calling program                                                        |

| www.akademi.itu<br>www.buzluca.info                                                                                  |                                                                                                                                                                        |                           |                          | © 2005-2022 Feza BUZLUCA A.18                                                                                        |

Computer Architecture

| Operation: [A<br>Used to copy th                                                                |                                                    |                                                                                                                                                                                                                            |  |  |  |  |

|-------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Sample syntax: LEA Table,A0<br>LEA (Table,PC),A0<br>LEA (-6,A0,D0.L),A6<br>LEA (Table,PC,D0),A6 |                                                    | ; register A0 will point to the<br>; beginning of Table<br>; calculates effective address of<br>; Table w.r.t. to PC, deposits it in A0.<br>; calculates A0+D0.L sign-extended<br>; to 32 bits minus 6, deposits it in A6. |  |  |  |  |

| Example:<br>ARRAY                                                                               | LEA ARRAY , A0<br>MOVE.B (A0)+, D1<br><br>DS.B 100 | ; Array address to A0<br>; Load first element of array to D1,<br>; increment A0 to point to next elmt.<br>; Define Storage (directive)                                                                                     |  |  |  |  |

| www.akademi.itu.edu.tr/bi<br>www.buzluca.info                                                   | uzluca                                             | © 2005-2022 Feza BUZLUCA A.19                                                                                                                                                                                              |  |  |  |  |

| Comput                                               | Computer Architecture                                                          |                                             |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Flow                                                 | Flow Control Instructions:                                                     |                                             |  |  |  |

| Bcc                                                  | Branch on condition cc                                                         |                                             |  |  |  |

| cc spe                                               | cc specifies the condition.                                                    |                                             |  |  |  |

| If o                                                 | If $cc = 1$ THEN [PC] $\leftarrow$ [PC] + d                                    |                                             |  |  |  |

| d: 8- c                                              | or 16-bit signed offset.                                                       |                                             |  |  |  |

| Remin                                                | der: When the instruction is being r                                           | un, PC points to the instruction after Bcc. |  |  |  |

| Synta                                                | x: Bcc <label></label>                                                         |                                             |  |  |  |

| Relativ                                              | ve size can be specified if needed: E                                          | BEQ.B (EQual) or BNE.W (Not Equal)          |  |  |  |

| If the                                               | If the size is not specified, the compiler computes the relative address of an |                                             |  |  |  |

| appropriate size based on the distance of the label. |                                                                                |                                             |  |  |  |

| Conditions (cc):                                     |                                                                                |                                             |  |  |  |

| BCC                                                  | branch on carry clear                                                          | branch if $C = 0$                           |  |  |  |

| BEQ                                                  | branch on equal                                                                | branch if Z=1                               |  |  |  |

| BGT                                                  | branch on greater than                                                         | branch if $(Z + (N \oplus V)) = 0$          |  |  |  |

| BHI                                                  | branch on higher than                                                          | branch if $(C + Z) = 0$                     |  |  |  |

| BGE                                                  | branch on greater than or equal                                                | branch if $(N \oplus V) = 0$                |  |  |  |

| BLT                                                  | branch on less than                                                            | branch if $(N \oplus V) = 1$                |  |  |  |

| BLS                                                  | branch on lower than or same                                                   | branch if $(C + Z) = 1$                     |  |  |  |

|                                                      | ademi.itu.edu.tr/buzluca<br>zluca.info                                         | © 2005-2022 Feza BUZLUCA A.20               |  |  |  |

| Computer Architecture                                                                                                                                                                                                                                                                     |                                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| DBcc Test condition, de                                                                                                                                                                                                                                                                   | cc Test condition, decrement, and branch                         |  |  |  |  |

| Syntax: DBcc Dn, <label></label>                                                                                                                                                                                                                                                          |                                                                  |  |  |  |  |

| Here, the label is a 16-bit relative address.                                                                                                                                                                                                                                             |                                                                  |  |  |  |  |

| 16 bits of Dn is used as a counter.                                                                                                                                                                                                                                                       |                                                                  |  |  |  |  |

| Operation:                                                                                                                                                                                                                                                                                |                                                                  |  |  |  |  |

| <pre>IF(condition cc false)     THEN [Dn] ← [Dn] - 1 (decrement loop counter)     IF [Dn] = -1 THEN instruction after DBcc (PC incremented by 2 in fetch cyc.)         ELSE [PC] ← [PC] + d (branch relative)     ELSE instruction after DBcc (PC incremented by 2 in fetch cycle.)</pre> |                                                                  |  |  |  |  |

| Example: Loop (10 times)                                                                                                                                                                                                                                                                  |                                                                  |  |  |  |  |

| MOVEQ                                                                                                                                                                                                                                                                                     | ; Start value 9, because exiting on D0=-1<br>; Inside the loop   |  |  |  |  |

| DBF D0,L1                                                                                                                                                                                                                                                                                 | ; Here, F: False, condition always false,<br>; branches if false |  |  |  |  |

| www.akademi.itu.edu.tr/buzluca<br>www.buzluca.info                                                                                                                                                                                                                                        | © 2005-2022 Feza BUZLUCA A.22                                    |  |  |  |  |

| Computer Architecture                                                                                                                                                                                                                                                             |                                                                         |                |                                                                                                                                                                                                                                                                                                                                                              |            |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| <b>Example:</b> Comparing Two Arrays (Are all elements equal?)<br>The first array starts at address ARRAY1, the second starts at address ARRAY2.<br>The arrays have 50 8-bit elements.<br>The contents of the arrays have been filled in before the program starts.<br>DBcc exits |                                                                         |                |                                                                                                                                                                                                                                                                                                                                                              |            |  |

| LOOP                                                                                                                                                                                                                                                                              | LEA<br>LEA<br>MOVE.W<br>SUBQ.W<br>CMPM.B<br>DBNE<br>TST.W<br>BMI<br>ENT | #1, D0         | ; Start addresses of the arrays<br>; A0 points to ARRAY1, A1 points to ARRAY2<br>; Size of arrays<br>; Decrement D0 by 1 for use in DBNE later<br>; Array elements compared as pair of bytes<br>; Test, decrement D0, and loop until not equal<br>; Why did loop exit? (D0?), sets N &Z based on D0<br>; Branch if neg. (If D0=-1 on exit, all elmts. equal) |            |  |

| EQUAL                                                                                                                                                                                                                                                                             |                                                                         |                |                                                                                                                                                                                                                                                                                                                                                              |            |  |

| ARRAY1<br>ARRAY2<br>SIZE                                                                                                                                                                                                                                                          | 20.2                                                                    | 50<br>50<br>50 | ; Allocate memory for elements of 1st array: 50B<br>; Allocate memory for elements of 2nd array: 50B<br>; Define constant in memory of length one word<br>; 50 elements in each array                                                                                                                                                                        |            |  |

| www.akao<br>www.buzl                                                                                                                                                                                                                                                              | demi.itu.edu.tr/b<br>uca.info                                           | uzluca         | © 2005-2022 Feza BUZ                                                                                                                                                                                                                                                                                                                                         | ZLUCA A.23 |  |