Advanced Digital Circuit Design - Asyncronous Sequential Digital Circuit Design

Prof. Dr. Berna Örs Yalçın

Istanbul Technical University Faculty of Electrical and Electronics Engineering Department of Electronics and Communication Engineering siddika.ors@itu.edu.tr

#### Asynch. vs. Synch.

- Asynchronous circuits don't use clock pulses

- state transitions by changes in inputs.

- Storage Elements:

- Clockless storage elements or

- · Delay elements.

- In many cases, as combinational feedback.

- $\cdot \rightarrow$  Normally much harder to design.

# Asynchronous Sequential Circuit

- In a gate-type circuit, the propagation delay that exists in the combinational circuit path from input to output provides sufficient delay along the feedback loop so that no specific delay elements are actually inserted in the feedback path

- difficult to design: Timing problems involved in the feedback path

- must attain a stable state before the input is changed to a new value

# Asynchronous Sequential Circuit

- Because of delays in the wires and the gates, it is impossible to have two or more input variables change at exactly the same instant of time without an uncertainty as to which one changes first.

- Therefore, simultaneous changes of two or more variables are usually prohibited.

- This restrictions means that only one input variable can change at any one time and the time between two input changes must be longer than the time it takes the circuit to reach a stable state.

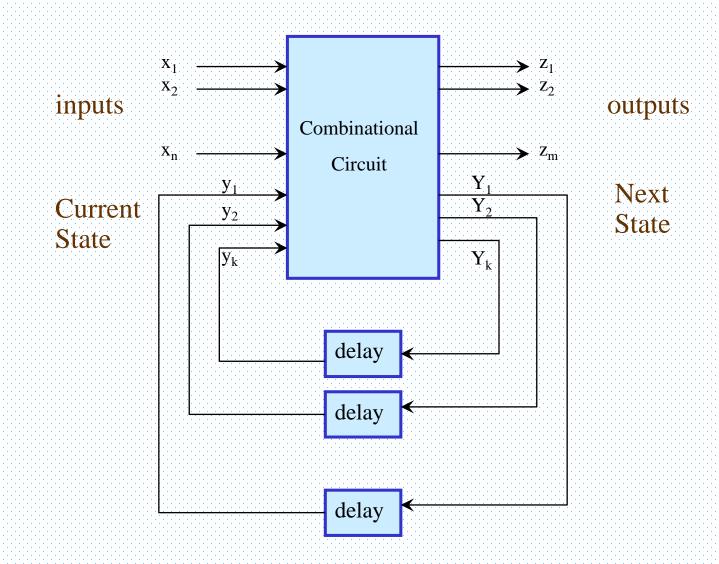

#### Asynch. Sequential Circuit

#### Asynch. Sequential Circuit

- y<sub>i</sub> = Y<sub>i</sub> in steady state (but may be different during transition)

- Simultaneous change in two (or more) inputs is prohibited.

- The time between two changes must be less than the time of stability.

#### Advantages and Disadvantages

#### Advantages:

- Low power

- High performance

- No need for clock

- Disadvantages:

- Complexity of design process.

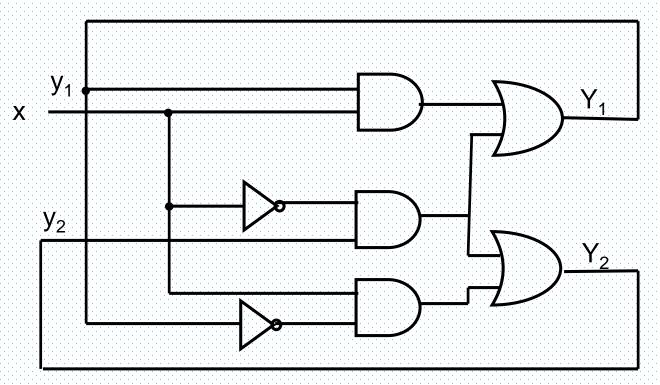

Find feedback loops and name feedback variables appropriately.

Find boolean expressions of Y<sub>i</sub>'s in terms of y<sub>i</sub>'s and inputs.

$$Y_1 = x.y_1 + x'.y_2$$

$Y_2 = x.y_1' + x'.y_2$

8

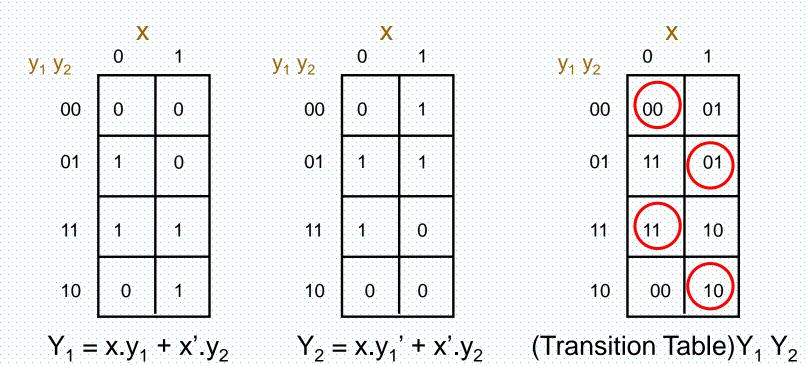

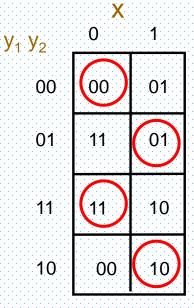

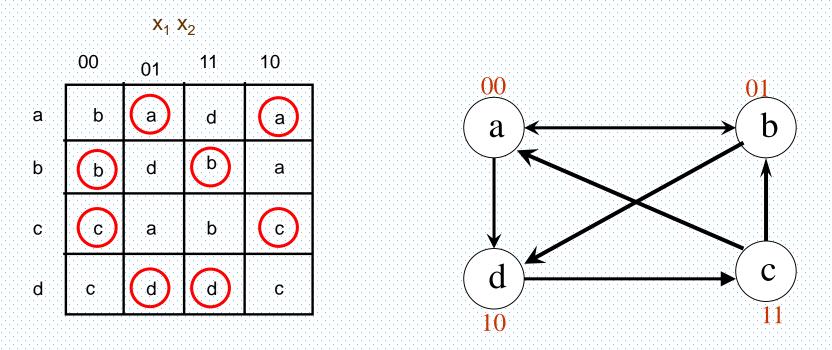

#### 3. Draw a map:

- rows: yi's

- columns: inputs

- entries: Yi's

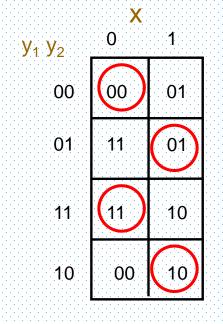

4. To have a stable state, Y must be = y (circled)

(Transition Table)  $Y_1 Y_2$

# At y<sub>1</sub>y<sub>2</sub>x = 000, if x: 0 → 1 then Y<sub>1</sub>Y<sub>2</sub>: 00 → 01 then y<sub>1</sub>y<sub>2</sub> = 01 (2<sup>nd</sup> row): stable.

In general, if an input takes the circuit to an unstable state, y<sub>i</sub>'s change until a stable state is found.

#### General state of circuit:

#### $\succ$ y<sub>1</sub>y<sub>2</sub>x:

- There are 4 stable states:

- > 000, 011, 110, 101

- and 4 unstable states.

#### State Table

#### - As synchronous:

| present | next state    |  |  |  |

|---------|---------------|--|--|--|

| state   | X = 0 $X = 1$ |  |  |  |

| 00      | 00 01         |  |  |  |

| 01      | 11 01         |  |  |  |

| 11      | 00 10         |  |  |  |

| 10      | 11 10         |  |  |  |

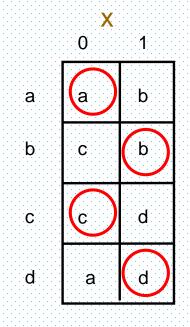

#### Flow Table

- As Transition Table (but with symbolic states):

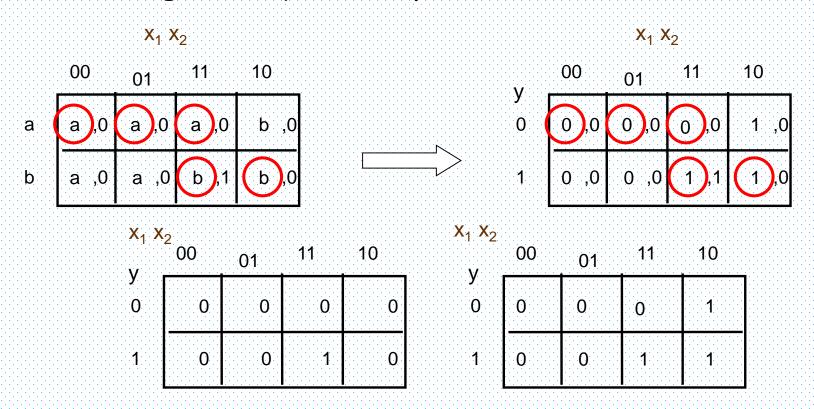

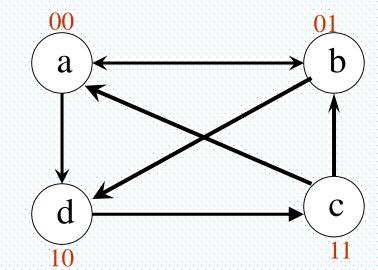

### Flow Table: Example 2

- Two states, two inputs, one output.

- Each row has more than one stable state.

- $\blacktriangleright \quad \text{If } x_1 = 0, \text{ state is a.}$

- > If  $x_1x_2 = 00$  →  $x_1x_2 = 10$ , then state becomes b.

- For  $x_1x_2 = 11$ , state is either a or b.

- > If previously in  $x_1x_2 = 01$ , keeps state a,

- > If previously in  $x_1x_2 = 10$ , keeps state b.

- Reminder: cannot go from 00 to 11.

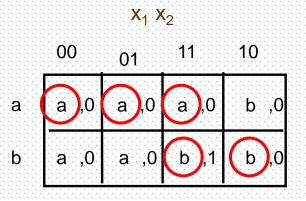

- From flow table to circuit:

Assign a unique binary value to each state,

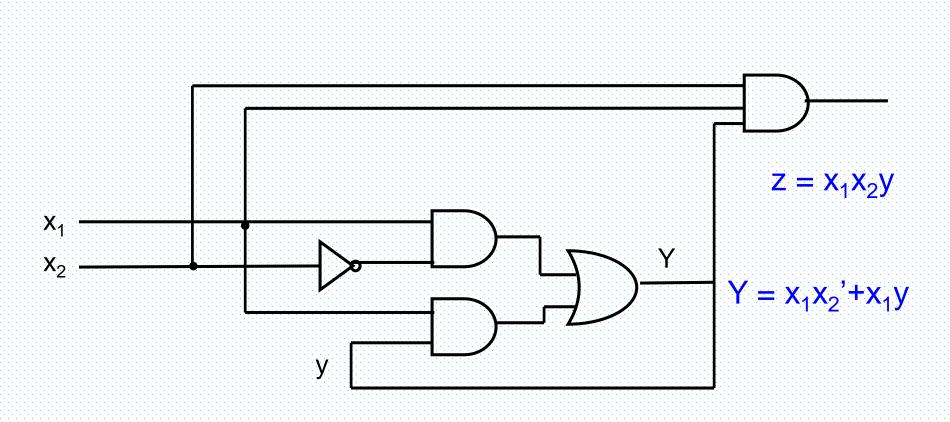

Map for output z  $(=x_1x_2y)$

Map for output Y  $(=x_1x_2'+x_1y)$

# Circuit Diagram

16

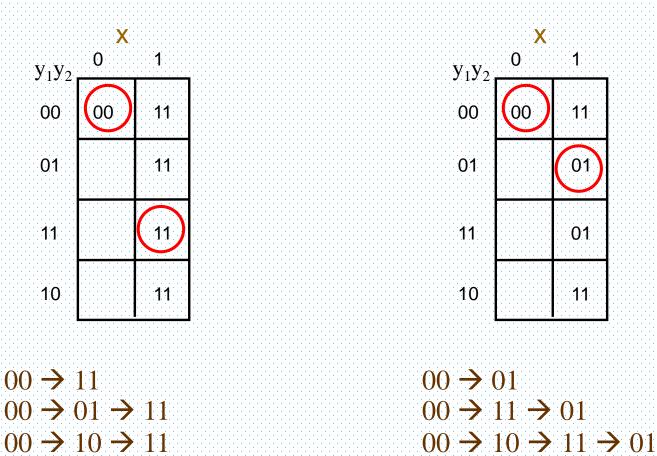

#### **Race Condition**

- If two (or more) state variables change in response to a change in an input, there is a race condition.

- E.g. from 00 to 11, due to delays  $00 \rightarrow 01 \rightarrow 11$  OR  $00 \rightarrow 10 \rightarrow 11$ .

# Critical Race:

If final steady state depends on the order of changes in state vars.

#### Race: Examples

Х

Noncritical Cases:

#### Race: Examples

Critical Cases:

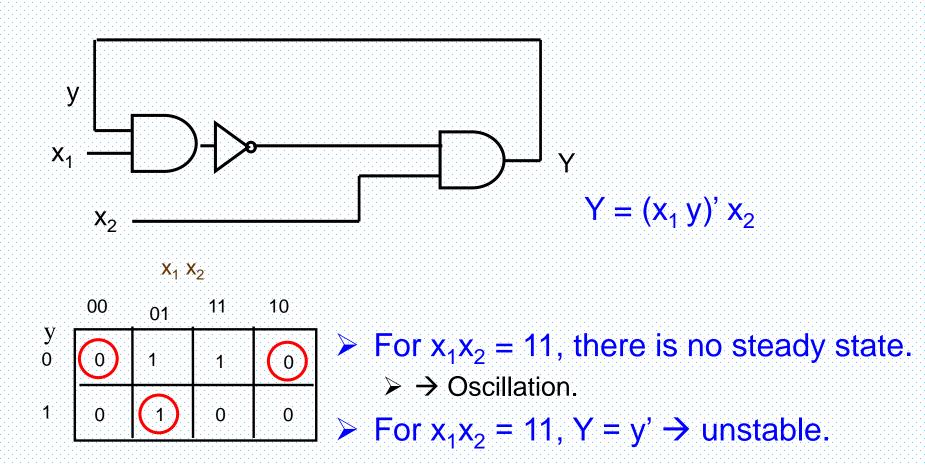

#### Instability

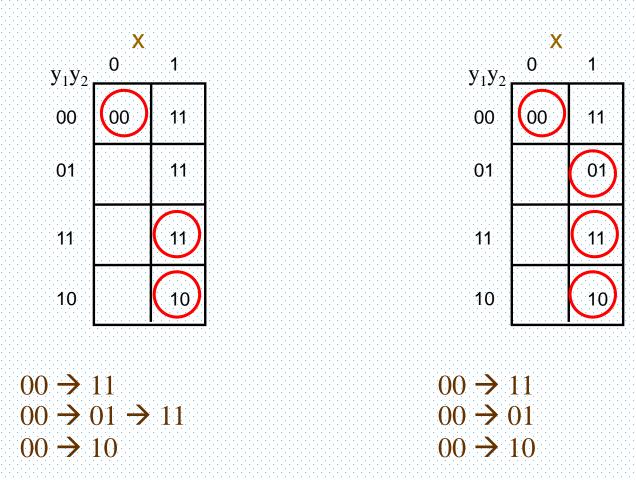

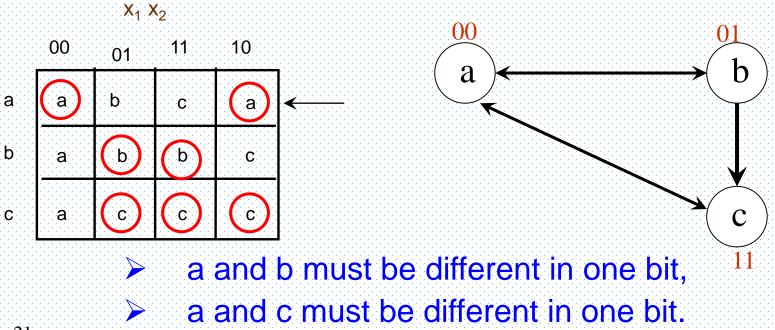

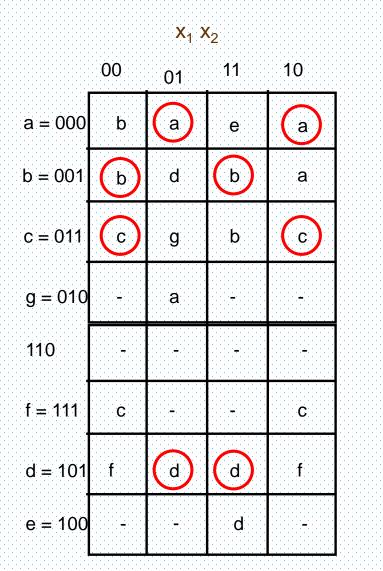

## No-Race State Assignment

- Must assign binary values to states such that:

- one change in an input may not cause two changes in state variables.

- (because due to delays, one of the variable change sooner and may stay in an unwanted stable state).

- From a, if  $x_1x_2 = 10 \rightarrow 11$ , must go to c and stay there.

- But by the following assignment, it may go to b and stay there.

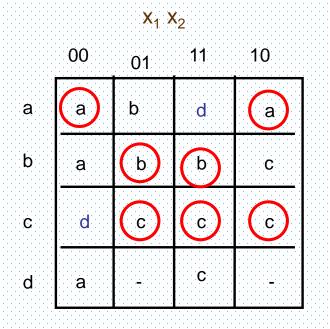

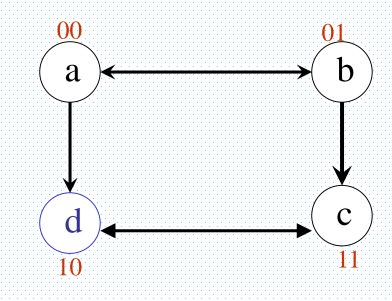

## No-Race State Assignment

- Impossible  $\rightarrow$  add one more row.

$\succ$

22

- d is an intermediate (unstable) state.

- means any value can be assigned (Except d=10).

# Example 2

➢ If there were no diagonal transition, it would be possible

➢ Impossible → add some more rows.

# Example 2

$\mathbf{b}$

$\mathbf{\mathbf{b}}$

$\mathbf{b}$

24

|                     | 00 | 01 | 11 | 10 |

|---------------------|----|----|----|----|

| У <sub>3</sub><br>0 | а  | b  | с  | g  |

| 1                   | е  | d  | f  | 0  |

$y_1 y_2$

- b is adjacent to a, c, d

- $c \rightarrow a$  through g

- > $a \rightarrow d$  through e

- $d \rightarrow c$  through f

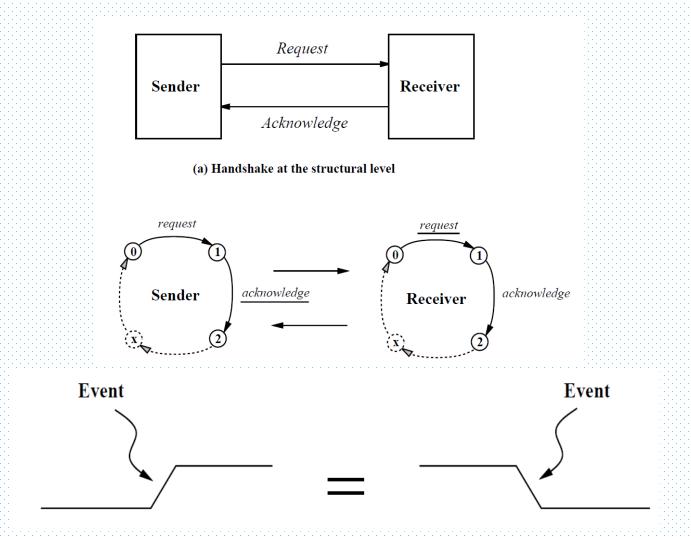

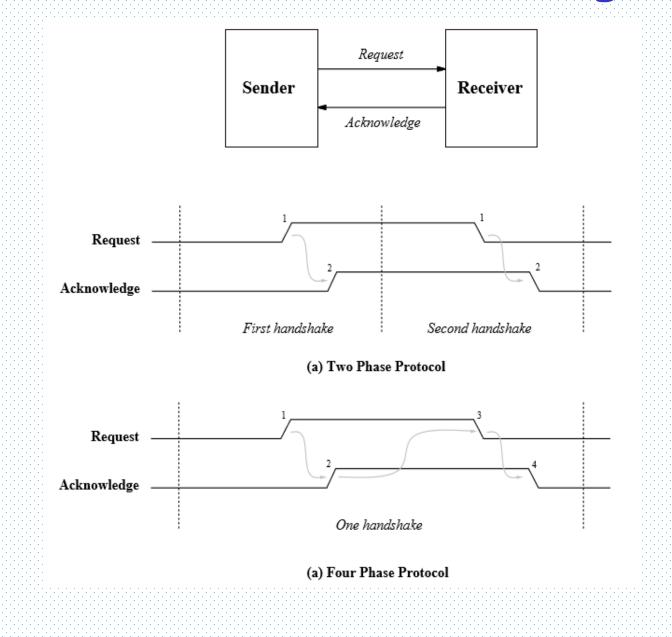

# Two Phase Signalling Protocol

The only thing that is important is that there is an event on the signal, that it changes value, not what it changes value to.

# Two versus Four Phase Signalling

26

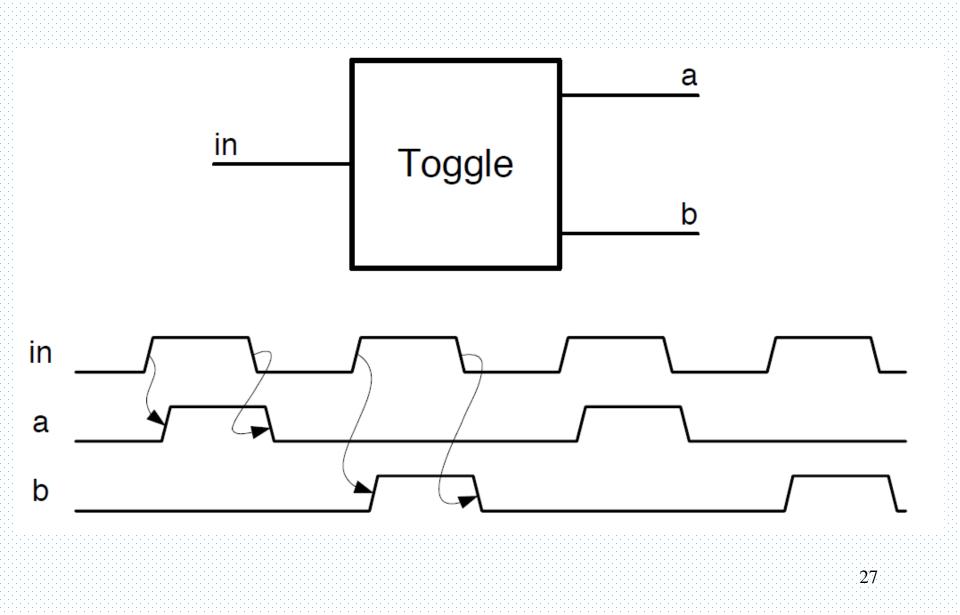

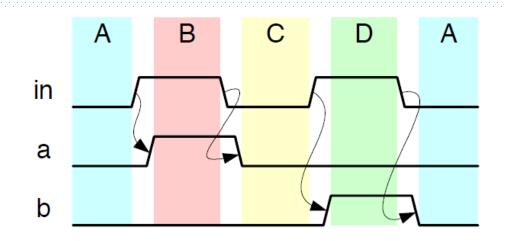

# Toggle Circuit

# Toggle Circuit Flow Table

| State | Nex        | t (in)     | Out<br>(a,b) |

|-------|------------|------------|--------------|

|       | 0          | 1          |              |

| А     | A          | В          | 00           |

| В     | С          | B          | 10           |

| С     | $\bigcirc$ | D          | 00           |

| D     | А          | $\bigcirc$ | 01           |

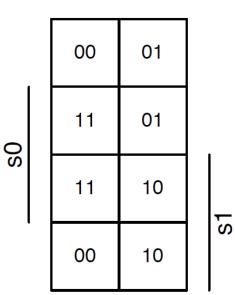

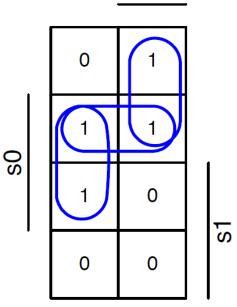

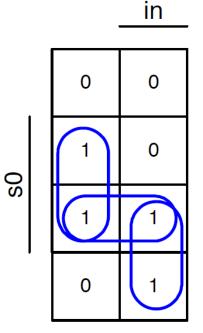

## Karnaugh Map of the State Variables

| State | Code | Nex        | t (in) | Out   |

|-------|------|------------|--------|-------|

| Sidle |      | 0          | 1      | (a,b) |

| А     | 00   | A          | В      | 00    |

| В     | 01   | С          | B      | 10    |

| С     | 11   | $\bigcirc$ | D      | 00    |

| D     | 10   | A          |        | 01    |

in

in

s1

29