### INTERNAL STRUCTURES OF ELECTRONIC DIGITAL CIRCUTS

- So far, we have seen abstract logic gates such as AND, OR, NAND, NOT, etc.

- There are many different ways of implementing a logic gate as an electronic circuit.

- In this lecture, we will discuss how different types of transistors are used to design electronic logic circuits.

- In digital circuits, transistors are always used as switches (ON or OFF).

- First, we introduce the bipolar junction transistor (BJT). A bipolar junction transistor is a three-terminal device that, in most logic circuits, acts like a current-controlled switch.

- Then, we will introduce the MOSFET (metal-oxide-semiconductor fieldeffect transistor) or simply the MOS transistor, which is used by almost all new integrated circuits.

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

11.1

Digital Circuits

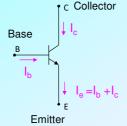

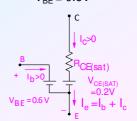

### Bipolar Junction Transistor:

The Base is the control terminal.

• State 1 (OFF)  $V_{BE} < 0.6V$ :

If no current is flowing into the base, then no current can flow from the collector to the emitter (OFF).

• State 2 (ON) V<sub>BE</sub> ≥ 0.6V:

However, if current is flowing from the base to the emitter, then current is also enabled to flow from the collector to the emitter (ON).

npn Bipolar Transistor: Transistor is cut off (OFF) Transistor is saturated (ON)  $V_{\text{RF}} < 0.6V \qquad \qquad V_{\text{RF}} \ge 0.6V$

http://akademi.itu.edu.tr/en/buzluca/

http://www.buzluca.info

2011 - 2023 Feza BUZLUCA

11.2

### Digital Circuits

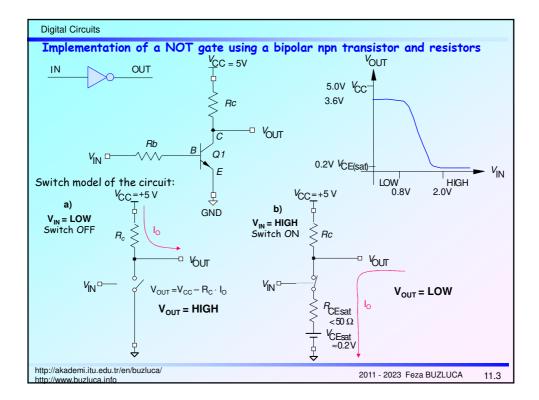

## TTL (Transistor - Transistor) Logic Family

- Transistor-transistor logic (TTL) is a class of digital circuits built from bipolar junction transistors (BJTs) and resistors.

- Actually, there are many different TTL families (such as LS, ALS, L, F), with a

range of speed, power consumption, and other characteristics.

- Their current and voltage values can be found in data catalogs.

- The circuit examples in this section are based on a representative TTL family, Low-power Schottky (LS or LS-TTL).

- Although TTL has been largely replaced by CMOS (which we will discuss later), you may encounter TTL components in your labs; therefore, we will cover basic TTL concepts in this course.

# Digital Circuits

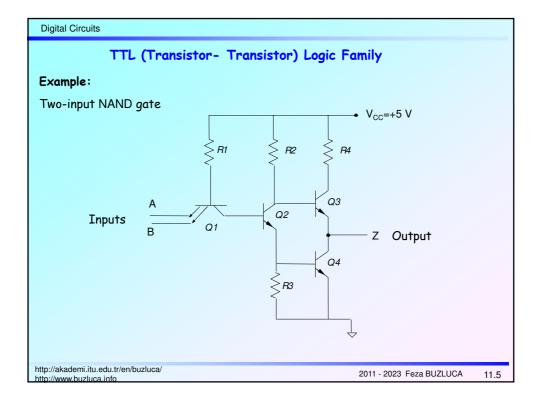

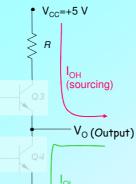

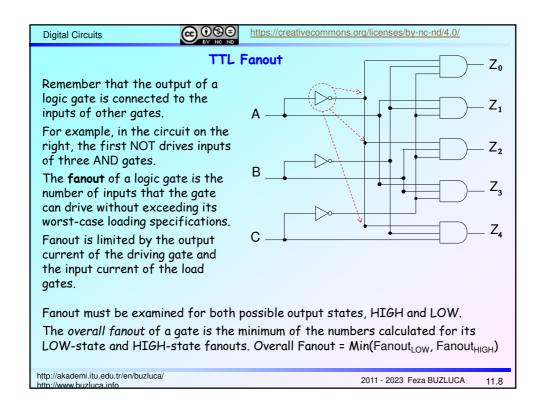

### Operation of the Output Stage of a TTL Gate

(sinking)

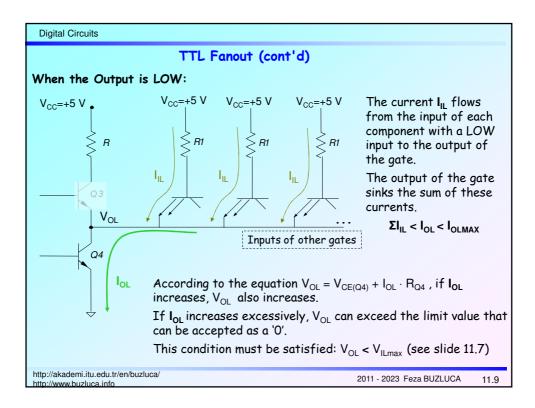

• Output is "O" (LOW):  $Q_4$  is ON,  $Q_3$  is OFF. In this case, the current  $I_{OL}$  flows into the output. The output is said to be sinking current.

$$V_{OL} = V_{CE(Q4)} + I_{OL} \cdot R_{Q4}$$

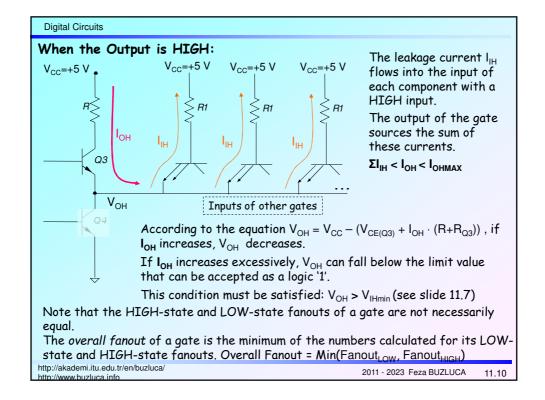

• Output is "1" (HIGH):  $Q_3$  is ON,  $Q_4$  is OFF. In this case, the current  $I_{OH}$  flows out of the output. The output is said to be sourcing current.

$$V_{OH} = V_{CC} - (V_{CE(Q3)} + I_{OH} \cdot (R + R_{Q3}))$$

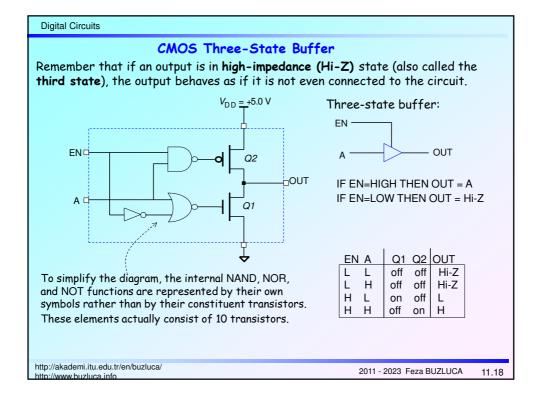

- If both Q<sub>3</sub> and Q<sub>4</sub> are OFF, the output is in the high-impedance (Hi-Z) state.

- It is also called the third state (High, Low, Hi-Z).

- In this state, the output behaves as if it is not even connected to the circuit.

- The output is isolated from the line it was connected to.

The specifications guarantee that under all normal operating conditions, a logic 1 output voltage will always be greater than 2.4 V and a logic 0 output less than 0.4 V.

For TTL components  $V_{OL(MAX)} = 0.4V$   $V_{OH(MIN)} = 2.4V$  (see slide 11.7)

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2023 Feza BUZLUCA

11.6

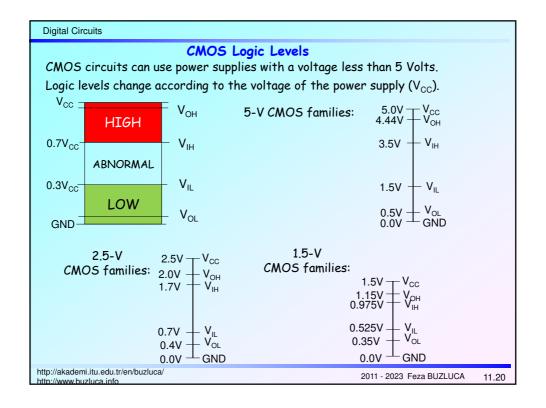

#### **Digital Circuits** TTL Logic Levels Abstract logic elements process binary digits, 0 and 1. However, real logic circuits process electrical signals such as voltage levels. In any logic circuit family, there is one range of voltages that is interpreted as logic 0 and another nonoverlapping range that is interpreted as logic 1. TTL circuits are connected to 5-volt power supply (Vcc=5V). Logic levels of a standard TTL unit: $V_{CC}$ V<sub>OHmin</sub>: The minimum output voltage produced in the HIGH state. HIGH V<sub>IHmin</sub>: The minimum input voltage guaranteed to be recognized as a HIGH. 2.4V $V_{OHmin}$ V<sub>ILmax</sub>: The maximum input voltage guaranteed to $-V_{\rm IHmin}$ 2.0V be recognized as a LOW. **ABNORMAL** $V_{\text{OL}\text{max}}\!\!:$ The maximum output voltage produced in the LOW state. $V_{\text{ILmax}}$ 0.8V LOW $V_{OLmax}$ 0.4V 0.0V **GND** http://akademi.itu.edu.tr/en/buzluca/ 2011 - 2023 Feza BUZLUCA 11.7

**Digital Circuits**

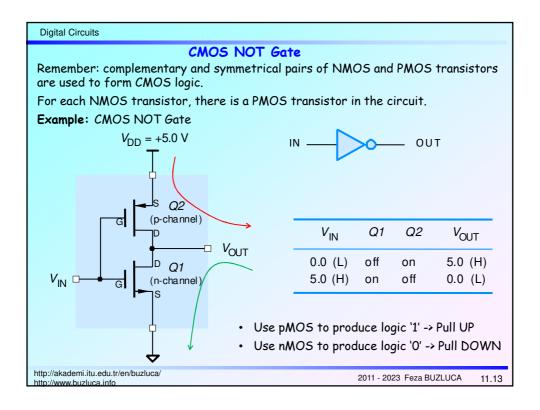

### CMOS (Complementary MOS) Logic Family

CMOS logic performs logic functions using a combination of MOSFETs (Metal-Oxide-Semiconductor Field-Effect Transistors).

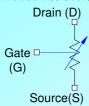

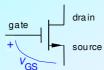

A MOS transistor can be modeled as a 3-terminal device that acts like a voltage-controlled resistor.

The voltage from Gate to Source ( $V_{GS}$ ) controls the resistance between Drain and Source ( $R_{DS}$ ).

- If the transistor is OFF,  $R_{DS} \ge 1M\Omega$  (10<sup>6</sup> $\Omega$ )

- If the transistor is ON,  $R_{DS} \le 10\Omega$

There are two types of MOS transistors.

a) n-channel MOS: NMOS.

Increase  $V_{GS} \rightarrow decrease R_{DS}$

Normally: V<sub>GS</sub>≥0V

V<sub>GS</sub>

y<sub>GS</sub> source drain

b) p-channel MOS: PMOS.

Decrease  $V_{GS} o decrease R_{DS}$

Normally: V<sub>GS</sub> ≤ 0V

many. V<sub>GS</sub> = 0 V

11.11

http://akademi.itu.edu.tr/en/buzluca/ http://www.buzluca.info

2011 - 2023 Feza BUZLUCA

Digital Circuits

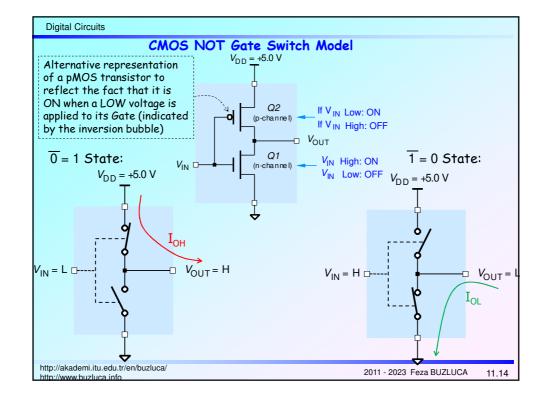

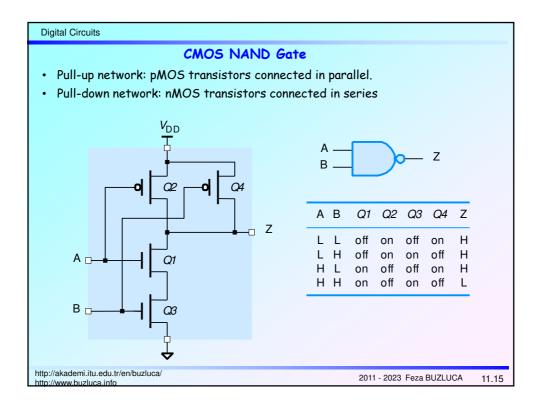

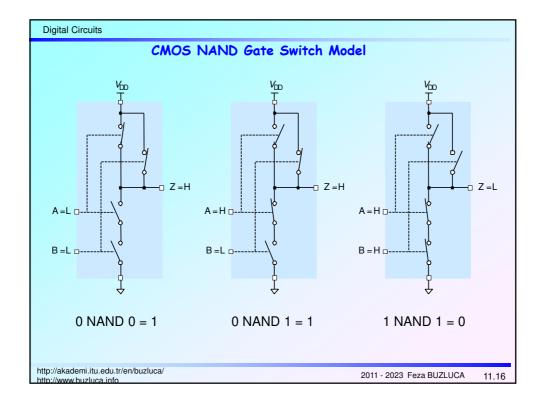

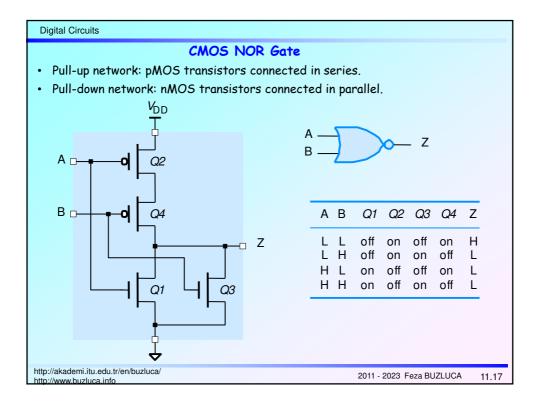

### CMOS Gate Implementation

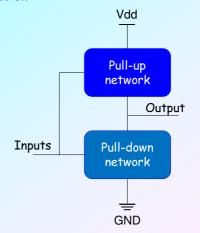

A CMOS logic gate consists of two parts:

- A. Pull-UP network: p-tree for pull-up

- It has to be connected to Vdd to pull up the output (logic 1).

- Build using pMOS connected in parallel or in series

- · Turns on when the function is true

- B. Pull-DOWN network: n-tree for pull-down

- It has to be connected to GND to pull down the output (logic 0).

- Build using nMOS connected in parallel or in series

- Turns on when the function is false

These two networks are operationally complements:

- · Pull-up network is complement of pull-down

- · Parallel -> series, series -> parallel

http://akademi.itu.edu.tr/en/buzluca/

2011 - 2023 Feza BUZLUCA

11.12