| Computer Architecture                                                                 | License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                                                                                                |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                       | <b>ect Memory Access (DMA)</b><br>d to transfer <u>large volumes of data</u> between I/O                                                                                                                                                   |

| Examples: Disk drive contr                                                            | ollers, graphics cards, network cards and sound cards.                                                                                                                                                                                     |

| DMA can also be used for                                                              |                                                                                                                                                                                                                                            |

| • intra-chip data transfer                                                            | in multi-core processors                                                                                                                                                                                                                   |

| · "memory to memory" cop                                                              | pying or moving of data                                                                                                                                                                                                                    |

| intervention of the process<br>traverse a path through th<br>• The CPU reads from I/C | med I/O and interrupt-driven I/O require the active<br>sor to transfer data, and any data transfer must<br>le processor.<br>J interface (or memory) and then writes to the memory<br>e programmed I/O and interrupt-driven I/O techniques. |

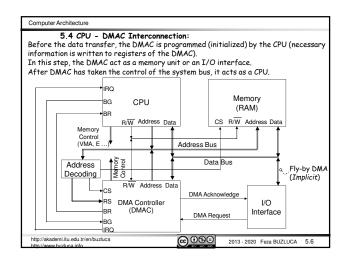

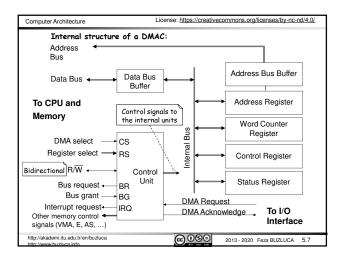

|                                                                                       | hardware module, called the <b>DMA Controller (DMAC)</b> .<br>PU, can generate addresses and initiate memory read or                                                                                                                       |

| • The CPU programs the D                                                              | DMAC and delegates the I/O operations to it.                                                                                                                                                                                               |

| • The CPU then continues                                                              | with other work.                                                                                                                                                                                                                           |

| • The DMAC performs all                                                               | I/O operations by taking control of the system bus. The                                                                                                                                                                                    |

DMAC is by taking control of the system bus. The data does not go through the CPU. @080 http://akademi.itu.edu.tr/en/buzluca

2013 - 2020 Feza BUZLUCA 5.1

| Computer Architecture                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2 Types of DMA Controllers:                                                                                                                                             |

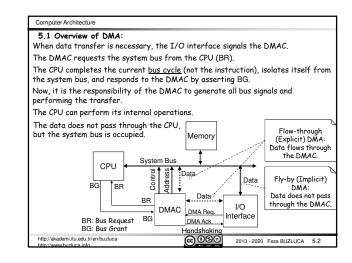

| a) Flow-through (Explicit) DMAC: The data, transferred between memory and the $\rm I/O$ interface passes through the DMAC.                                                |

| The DMAC first reads data into an internal register and then writes it to the<br>destination.                                                                             |

| b) Fly-by (Implicit) DMAC: The data does not pass through the DMAC.                                                                                                       |

| After the DMA controller gains access to the bus, it ouputs the source (or destination) address and other control signals (R/W, VMA, etc.).                               |

| It activates the memory and the I/O interface at the same time.                                                                                                           |

| So, it initiates a read and a write cycle simultaneously. The data is read from<br>the source address, and written to the destination in <b>one clock cycle</b> .         |

| Therefore, the fly-by technique can transfer data faster than the flow-<br>through technique.                                                                             |

| However, this technique implies that either the source or destination does not<br>require an address because the DMAC can only put one address on the bus at<br>any time. |

| So, memory-to-memory transfers (between two different addresses) are not<br>possible in this mode.                                                                        |

| Therefore, a fly-by DMAC can only transfer data between an I/O port and a memory address.                                                                                 |

| http://akademi.itu.edu.tr/en/buzluca                                                                                                                                      |

| 5.3 DMA Transfer Modes:<br>a) Burst mode (Block Transfer Mode): Once the DMA controller takes the control for the system bus, it transfers all bytes of data in the data block before releasing control of the system bus back to the CPU.<br>The CPU determines the size of the block in the initialization process.<br>The DMAC may render the CPU inactive for a relatively long time.<br>This mode is useful for loading programs or data files into memory, because the |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The DMAC may render the CPU inactive for a relatively long time.<br>This mode is useful for loading programs or data files into memory, because the                                                                                                                                                                                                                                                                                                                          |

| This mode is useful for loading programs or data files into memory, because the                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CPU needs this data to continue its work.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| b) Cycle stealing: The DMAC requests the bus as in the burst mode. When it is<br>granted to access the bus by the CPU, the DMAC transfers only one word and giv<br>the control of the bus back to the CPU.                                                                                                                                                                                                                                                                   |

| The DMAC continually issues requests, transferring one word of data per request<br>until it has transferred its entire block.                                                                                                                                                                                                                                                                                                                                                |

| This technique is suitable for systems in which the CPU should not be disabled for long time.                                                                                                                                                                                                                                                                                                                                                                                |

| The CPU needs to access the memory in instruction and operand fetch cycles, an<br>needed, for operand write operations.                                                                                                                                                                                                                                                                                                                                                      |

| In decode and execution cycles, the CPU can operate without accessing the memory while the DMAC performs the data transfer.                                                                                                                                                                                                                                                                                                                                                  |

080 http://akademi.itu.edu.tr/en/buzluca 2013 - 2020 Feza BUZLUCA 5.4

| DMA Transfer Modes: (cont'd)                                              |                                                                                   |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| b) Cycle stealing: (cont'd)                                               |                                                                                   |

| This mode interleaves instruction e DMAC.                                 | execution by the CPU and data transfer by the                                     |

| The rate of data transfer is slower                                       | than in burst mode.                                                               |

| c) Transparent mode (Hidden DMA                                           | <b>\):</b>                                                                        |

| The DMAC (or an additional hardwo<br>only when the processor is not using | are unit) monitors the CPU and uses the bus<br>g it.                              |

|                                                                           | he processor is executing an instruction<br>cycles to perform a word transfer, it |

| The processor is not slowed down.                                         |                                                                                   |

| The transfer of the data block can                                        | take longer than other modes.                                                     |

| The disadvantage is that the hardw<br>using the system.                   | vare needs to determine when the CPU is not                                       |

| Burst mode and cycle stealing are t the DMA.                              | he most commonly used transfer modes of                                           |

| http://akademi.itu.edu.tr/en/buzluca                                      | 2013 - 2020 Feza BUZLUCA 5.5                                                      |

| Computer Architecture                                                                                                                                                                                                                                                                       | Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

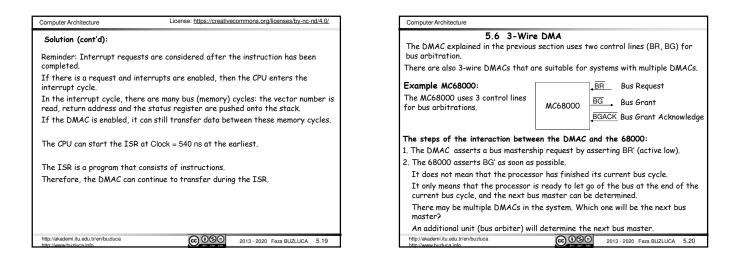

| 5.5 Steps of data transfer in the DMA technique (cont'd)                                                                                                                                                                                                                                    | 5.5 Steps of data transfer in DMA technique (cont'd)                                                                                                                                                                                                                                                                                                                                                            |

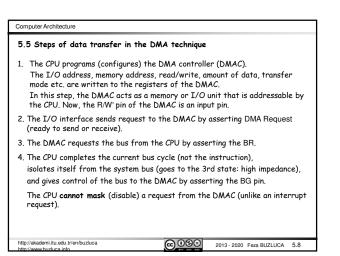

| 5. Now, the new bus master is the DMAC. It is the responsibility of the DMAC to provide all necessary signals to address the memory as the CPU does.<br>In this step the R/W pin of the DMAC is an output.<br>The DMAC puts the address, R/W and other necessary signals on the system bus. | <ol> <li>If the I/O interface persists in its transfer request (DMA Request), the<br/>DMAC keeps the BR active.</li> <li>Burst mode: The DMAC maintains BR (active) until the whole block is<br/>completed.</li> </ol>                                                                                                                                                                                          |

| <ul> <li>bus.</li> <li>a) Fly-by (implicit) DMA:</li> <li>The DMAC sends a DMA Acknowledge to the I/O interface.</li> <li>The I/O interface either reads the data from the data bus or puts the data on the data bus.</li> <li>b) Flow-through (explicit) DMA:</li> </ul>                   | Cycle stealing: After transferring one word, the DMAC deasserts the BR,<br>allowing the CPU to use the system bus, and then asserts the request again.<br>While the DMAC is transferring the data, the CPU can perform its internal<br>operations, which do not need the access to the system bus, such as<br>instruction decoding and operations on register (Compare to polling and<br>interrupt-driven I/O). |

| The DMAC sends a DMA Acknowledge to the I/O interface.<br>The DMAC reads the data from the I/O interface and writes it to memory<br>or<br>The DMAC reads the data from memory, sends a DMA Acknowledge to the I/O<br>interface, and writes the data to the I/O interface.                   | 7. If there are no a new requests from the I/O interface (DMA Request is not active) or the entire block has been transferred (the word counter of the DMAC is zero), the DMAC isolates itself from the system bus, i.e. its control lines go to the 3rd state (high impedance). The DMAC deasserts BR. The CPU gets control of the system bus back.                                                            |

| http://akademi.itu.edu.tt/enbuzluca                                                                                                                                                                                                                                                         | http://akademi.itu.edu.tr/en/buzluca COGO 2013 - 2020 Feza BUZLUCA 5.10                                                                                                                                                                                                                                                                                                                                         |

| Computer Architecture                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5 Steps of data transfer in DMA technique (cont'd)                                                                                                                                                     |

| <ol> <li>After finishing the transfer of a block, the DMAC can send an interrupt<br/>request to the CPU to inform it of the completion of the transfer (if it is<br/>configured in this way).</li> </ol> |

| The CPU can read the internal registers of the DMAC to get information about the previous transfer (how many words have been transferred, are there any errors?).                                        |

| Here, interrupts are not involved in requesting the bus and data transfer.                                                                                                                               |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

|                                                                                                                                                                                                          |

| http://akademi.itu.edu.tr/en/buzluca                                                                                                                                                                     |

|                                                                                           | I/O using DMA Technique                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:                                                                                  |                                                                                                                                                                                                  |

|                                                                                           | has the following 5 states (cycles):                                                                                                                                                             |

| <ol> <li>Instruction fetch: 60 ns, 2. I</li> <li>Execution: 30 ns, 5. Interrup</li> </ol> | nstruction Decode: 20 ns, 3. Operand fetch: 60 ns<br>t: 200 ns.                                                                                                                                  |

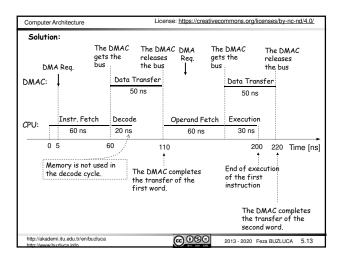

| Assume that the CPU accesses fetch cycles but not in the deco                             | the memory in the instruction fetch and operand ode and execution cycles.                                                                                                                        |

| words from the I/O interface t<br>The DMAC type is <b>fly-by</b> (impli                   | e (BR, BG) DMAC that is configured to transfer 10<br>to the memory using the cycle-stealing technique.<br>cit). Data does not pass through the DMAC.<br>O interface access times are both 50 ns. |

| Assume that we start a clock (C<br>that consists of 10 instructions                       | Clock = 0) when the CPU begins to run a program                                                                                                                                                  |

| When the CPU is in the instruct<br>5ns), the DMAC attempts to sto                         | tion fetch cycle for the first instruction (Clock = art the data transfer.                                                                                                                       |

| a. When (Clock =?) will the DM                                                            | AC complete the transfer of the first word? Why?                                                                                                                                                 |

| b. When (Clock =?) will the CPL                                                           | J finish the first instruction? Why?                                                                                                                                                             |

|                                                                                           | AC complete the transfer of all 10 words? When<br>f the entire program with 10 instructions?                                                                                                     |

|                                                                                          | irrent bus cycle (instruction fetch) and isolates<br>The DMAC transfers the first word.                                                |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Since the DMAC type is fly-l<br>Clock = $60 + 50 = 110$                                  | <b>by</b> (implicit), data is transferred in 50 ns.<br>Ons                                                                             |

| <ul> <li>b) Instruction decoding and e</li> <li>DMA transfers.</li> </ul>                | execution cycles of the CPU can run in parallel with                                                                                   |

|                                                                                          | •                                                                                                                                      |

| c) During one instruction cycl<br>10 words are transferred in 5<br>Clock = 5 * 220 = 110 |                                                                                                                                        |

| After the transfer of the 10                                                             | rds, the CPU can run 5 instructions.<br>words, the CPU runs each instruction in 170 ns.<br>n cycle is 60+20+60+30= 170 ns.<br>= 1950ns |

| Compare these times to the i                                                             | nterrupt-driven I/O example on slide 4.17.                                                                                             |

| http://akademi.itu.edu.tr/en/buzluca                                                     | @ 0 0 0 0 2013 - 2020 Feza BUZLUCA 5.14                                                                                                |

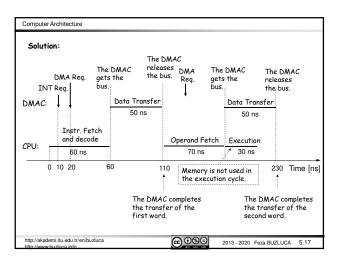

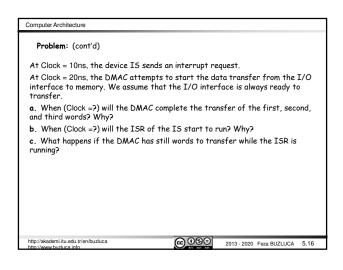

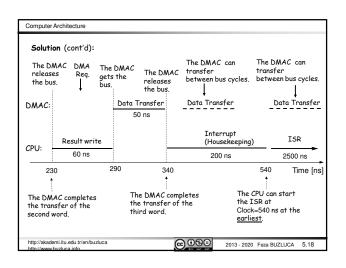

## Computer Architecture Example 2: DMA and Interrupt Problem: The instruction cycle of a CPU has the following 5 states (cycles) with the given durations: 1. Instruction fetch and decode: 60 ns, 2. Operand fetch: 70 ns, 3. Execution: 30 ns, 4. Result write: 60 ns, 5. Interrupt: 200 ns. Only in the "3. Execution" cycle, the CPU does not access memory. The CPU uses memory in the other cycles (1, 2, 4, 5). The memory access time and I/O interface access time are both 50 ns. In this system there is a single interrupt source (IS). The duration of its interrupt service routine (ISR) is 2500ns. In this system there is a 2-wire DMAC that is configured to transfer words from the I/O interface to the memory using the cycle-stealing technique. The DMAC type is fly-by (implicit). Data does not pass through the DMAC. Assume that we start a clock (Clock = 0) when the CPU begins to run the program. http://akademi.itu.edu.tr/en/buzluca 0000 2013 - 2020 Feza BUZLUCA 5.15

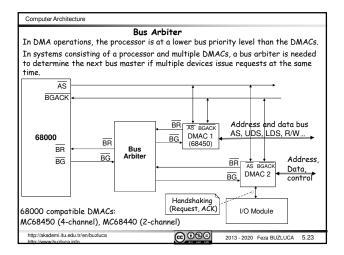

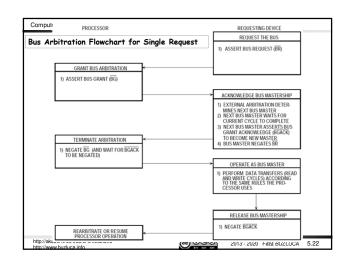

## Computer Architecture The operation of a DMAC in a 68000-based system: (cont'd) 3. If there is more than one DMAC in the system, the bus arbiter circuitry determines the next bus muster. Upon receiving BG, the requesting device waits until the current bus cycle is completed (AS, DTACK, and BGACK must be negated). The negation of AS indicates that the previous bus master has completed its cycle. (No device is allowed to assume bus mastership while AS is asserted.) The negation of DTACK indicates that neither memory nor peripherals are using the bus The negation of BGACK indicates that the previous master has released the bus. 4. The new bus master asserts and maintains BGACK during the entire bus cycle (or cycles) for which it is bus master. The BR of this DMAC is negated after BGACK is asserted. Hence, another DMAC in the system can issue its request. 5. When the data transfer is complete, the DMAC relinquishes control of the bus by negating BGACK. The processor cannot access the bus while BGACK is asserted http://akademi.itu.edu.tr/en/buzluca 000 2013 - 2020 Feza BUZLUCA 5.21

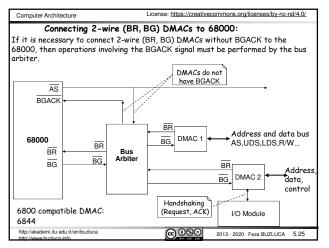

## Computer Architecture

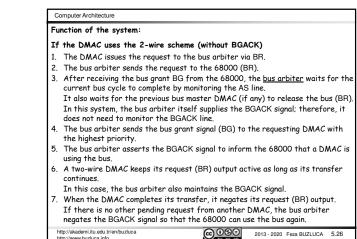

- If the DMAC uses the 3-wire scheme (with BGACK) (e.g., MC68450)

- 1. The DMAC issues the request to the bus arbiter via BR.

- 2. The bus arbiter sends the request to the 68000 (BR).

- The bus arbiter receives the grant signal (BG) from the 68000 and sends this signal to the requesting DMAC with the highest priority.

After receiving the bus grant BG, the DMAC monitors the AS and BGACK

- signals to determine when it may assume mastership of the bus.

AS and BGACK must be negated to indicate that the previous cycle is complete and the previous bus master has released the bus.

5. When this condition is met, the DMAC asserts BGACK to inform the processor and other DMACs that it has taken control of the bus.

As the new bus master, the DMAC deaserts its BR output to allow the external

- arbiter to begin arbitration for the next bus master. It maintains BGACK until the transfer is complete. As the bus master, it is responsibility of this DMAC to supply all address and control signals (AS, UDS, LDS, VMA, R/W, ...). 6. When all DMACs complete their transfers, the BGACK input of the 68000 is

- negated. Now, the 68000 can use the system bus again. http://dedomilut.edu.tir/infuturusa http://dedomilut.edu.tir/infuturusa 2013-2020 Feza BUZLUCA 5.24

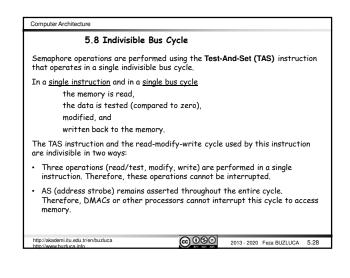

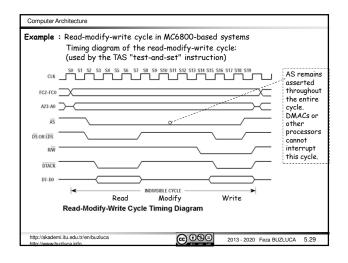

| TAS                              | Test                                             |                                                | and (MC(800)                                                                                                                                                                                                               |

|----------------------------------|--------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Form                             |                                                  | TAS <ea></ea>                                  | rand (MC6800)                                                                                                                                                                                                              |

| Opero<br>Tests<br>The n<br>These | ation:<br>s the oper<br>nost signi<br>e operatio | [CCR] ←<br>and: According<br>ficant bit (7) or | tested([operand <ea>]); [destination: <ea>(7)] ← 1<br/>the value of data, Z and N flags are modified.<br/>f the operand is set to 1 (made negative).<br/>le (single instruction, single bus cycle).<br/>vations.</ea></ea> |

| Exam                             | ple1: Crit                                       | ical section acc                               | ess without TAS instruction (dangerous!)                                                                                                                                                                                   |

| TEST                             | TST.B                                            |                                                | (Divisible)                                                                                                                                                                                                                |

| CRITIC                           | BMI<br>AL OR.B                                   | #\$80,FLAG                                     | If negative (MSB=1?)<br>Semaphore is set<br>Critical section                                                                                                                                                               |

| END                              | CLR.B                                            | FLAG                                           | Semaphore is cleared (unlock)                                                                                                                                                                                              |

| Examp                            | le2: Crit                                        | ical section acc                               | ess using the TAS instruction (correct)                                                                                                                                                                                    |

| TEST                             | TAS<br>BMI                                       | FLAG<br>TEST                                   | Tests the semaphore and sets it if necessary                                                                                                                                                                               |

| CRITIC                           | AL                                               |                                                | Critical section                                                                                                                                                                                                           |

| END                              | CLR.B                                            | FLAG                                           | Semaphore is cleared (unlock)                                                                                                                                                                                              |

| http://aka                       | demi.itu.edu.tr                                  | /en/buzluca                                    | @ 0 8 0 2013 - 2020 Feza BUZLUCA 5.30                                                                                                                                                                                      |