| Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Appendix B: RISC (Reduced Instruction Set Computer) Processors:                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| RISC Features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Relatively small set of simple instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Relatively few, simple addressing modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| <ul> <li>Fixed-length, easily decoded instruction format</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| <ul> <li>No instructions that operate directly on memory, all operations performed<br/>within internal registers of the CPU.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Memory access only for load/store instructions (load-store architecture).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| <ul> <li>One instruction per clock cycle (owing to pipelining)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Hardwired rather than microprogrammed control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| <ul> <li>Other Characteristics:</li> <li>Not all of the features listed below are included in all RISC processors, and CISC processors may also include some of these features:</li> <li>A large number of registers (128-256) (Register File)</li> <li>Use of overlapped register windows to speed up procedure call and return</li> <li>Instruction pipeline that can be optimized for instructions</li> <li>Harvard architecture</li> <li>Compiler support for efficient translation of high-level language programs into</li> </ul> |  |  |  |  |  |

| machine language programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| www.akademi.itu.edu.tr/en/buzluca © 2005-2022 Feza BUZLUCA B.1<br>www.buzluca.info                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

## Computer Architecture

## Overlapped Register Windows:

Without needing a stack (memory access), this structure is used in procedure calls

• to provide passing of parameters and

• to avoid the need for saving and restoring register values.

Even though the processor has many registers, the programmer can only use a limited number of these at any given moment.

This set of registers that can be active at any given time are called a window.

When the program calls (and returns from) a subroutine, the window changes. Thus, the programmer accesses different registers.

Windows for adjacent procedures have overlapping registers that are shared to provide the passing of parameters and results. Local registers are used for local variables of the procedures.

If there are n registers in a window, when writing programs, only registers R0 through Rn-1 are used.

However, as the window changes, these numbers correspond to different physical registers.

Not all RISC processors use this structure (e.g., the MIPS processor does not).

## **Computer Architectur**

## Example:

- In the example below, the processor has 8 registers. However, a window has 5 registers, so at any given time, only 5 of these can be active.

- In programs, only R0-R4 are used, but as the window changes, these end up corresponding to different registers.

- In A, when the programmer reaches R0, the programmer has reached R0 of the processor.

- In B, when the programmer reaches R0, the programmer has reached R3 of the processor

| Local                                                                          | R7              | BR4     |                                        |  |  |

|--------------------------------------------------------------------------------|-----------------|---------|----------------------------------------|--|--|

| Registers {<br>of B                                                            | R6              | BR3     | window of procedure B (called program) |  |  |

|                                                                                | R5              | BR2     | ( (callee)                             |  |  |

| Shared                                                                         | R4              | BR1 AR4 |                                        |  |  |

| registers                                                                      | R3              | BR0 AR3 |                                        |  |  |

| Local<br>Registers {                                                           | R2              | AR2     | windows of procedure A (main program)  |  |  |

|                                                                                | R1              | AR1     | (caller)                               |  |  |

| of A                                                                           | R0              | AR0     |                                        |  |  |

| There are also global registers with fixed numbers that all procedures access. |                 |         |                                        |  |  |

| www.akademi.itu.eo<br>www.buzluca.info                                         | du.tr/en/buzluc | a       | © 2005-2022 Feza BUZLUCA B.3           |  |  |

| Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|--|--|

| Determining the number of registers:         G       : Number of global registers         L       : Number of local registers in each window         C       : Number of registers common to two windows         W       : Number of windows         Window size = L + 2C + G       (2*C because there are registers in common with the lower and upper window.)                                                                                                                       |                              |  |  |  |  |

| Number of registers = (L+C)W + G                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |  |  |  |  |

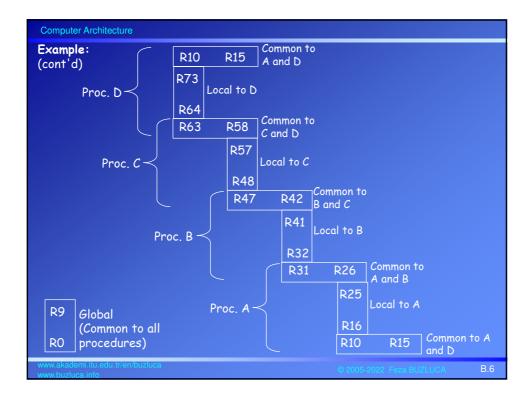

| The window structure is arranged in a circular fashion.<br>If the processor has 4 windows, when the 4th procedure calls a 5th procedure,<br>the 1st window (the oldest window, the one furthest back in the call nesting) is<br>saved to memory.<br>Then, the 1st window is used by the 5th procedure.<br>When returning, the data in memory is restored to the relevant window.<br><b>Example:</b><br>In the next example, we give the register structure of a processor with a total |                              |  |  |  |  |

| of 74 registers and a windows size of 32 registers which supports procedure calls to a nesting depth of 4.                                                                                                                                                                                                                                                                                                                                                                             |                              |  |  |  |  |

| In this example, we assume that as procedures are called, subsequent windows are allocated registers with higher numbers. In real processors (RISC 1, SPARC), subsequent windows are allocated registers with lower numbers.                                                                                                                                                                                                                                                           |                              |  |  |  |  |

| www.akademi.itu.edu.tr/en/buzluca                                                                                                                                                                                                                                                                                                                                                                                                                                                      | © 2005-2022 Feza BUZLUCA B.4 |  |  |  |  |

| Computer Architecture           |                                                                                                                        |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Example:                        |                                                                                                                        |

| Total of 74 regis               | sters                                                                                                                  |

| Global registers                | : G = 10 (R0-R9) (common to all procedures)                                                                            |

| R10-R73                         | : 64 registers divided into FOUR windows to accommodate procedures A-D. (W=4)                                          |

| Local registers                 | : L = 10                                                                                                               |

| Common register                 | <i>s</i> : 2*C = 6 + 6 =12                                                                                             |

| Window size                     | : L + 2C + G = 32 reg.                                                                                                 |

|                                 | nce there are 32 registers in a window, when writing a program in<br>e, each procedure uses register numbers R0 – R31. |

| Based on the loca<br>registers. | tion of the window, these numbers correspond to different physical                                                     |

| See: exemplary pr               | rogram in B.13                                                                                                         |

|                                 |                                                                                                                        |

|                                 |                                                                                                                        |

|                                 |                                                                                                                        |

| www.akademi.itu.edu.tr/en       | /buziuca @ 2005-2022 Feza RUZI LICA B.5                                                                                |

| Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>RISC Processor Example: Berkeley RISC I</li> <li>32-bit address bus</li> <li>von Neumann architecture: Instruction and data are stored in the same memory.</li> <li>8-, 16-, or 32-bit data</li> <li>Fixed length (32-bit) instructions</li> <li>Total of 31 instructions</li> <li>Total of 138 registers (R0-R137),<br/>8 windows of 32 registers in each, 10 global registers (R0-R9)<br/>Local registers: 10, Common registers: 6+6=12</li> <li>3 addressing modes: register addressing, immediate addressing, relative addressing</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Instruction Formats:<br>1. Register mode:<br>2. Register mode:<br>2. Register mode:<br>2. Register mode:<br>2. Register mode:<br>2. Register mode:<br>31 2423 19 18 14 13 12 5 4 0<br>Opcode Rd Rs 0 Not used 52<br>2. Register mode:<br>2. Register mode:<br>31 2423 19 18 14 13 12 5 4 0<br>Opcode Rd Rs 0 Not used 52<br>2. Register mode:<br>2. Register mode:<br>31 2423 19 18 14 13 12 5 4 0<br>Opcode Rd Rs 0 Not used 52<br>2. Register mode:<br>2. Register mode:<br>31 2423 19 18 14 13 12 5 4 0<br>Opcode Rd Rs 0 Not used 52<br>2. Register mode:<br>2. Register mode:<br>31 2423 19 18 14 13 12 5 4 0<br>Opcode Rd Rs 0 Not used 52<br>2. Register mode:<br>2. Register mode:<br>3. R |  |  |  |  |

| www.akademi.itu.edu.tr/en/buzluca @ 2005-2022 Feza BUZLUCA B.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Computer Architecture                                                                                                                                                          |                                                        |       |       |       |         |                      |                       |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------|-------|-------|---------|----------------------|-----------------------|-----|

| 2. Register - ir                                                                                                                                                               | mmedia                                                 | te mo | de:   |       |         |                      |                       |     |

|                                                                                                                                                                                | 31                                                     | 24    | 23 19 | 18 14 | 4 13    | 12                   | 0                     |     |

|                                                                                                                                                                                | O                                                      | pcode | Rd    | Rs    | 1       | 52                   |                       |     |

|                                                                                                                                                                                |                                                        | 8     | 5     | 5     | 1       | 13                   |                       |     |

| <b>Example</b> : ADD I                                                                                                                                                         | Example: ADD R22, #150, R23 R23←R22+150 Immediate data |       |       |       |         | ۵                    |                       |     |

| Memory access instructions use Rs to specify a 32-bit address in a register<br>(pointer) and S2 to specify an offset. The location accessed is:<br>(32-bit address in Rs) + S2 |                                                        |       |       |       | er      |                      |                       |     |

| Example: LDL (R10)#5,R5 F                                                                                                                                                      |                                                        |       | R5←M[ | R10   | + 5] Lo | ad long: 32-bit dat  | ta transfer           |     |

| 3. PC Relative mode:                                                                                                                                                           |                                                        |       |       |       |         |                      |                       |     |

| Example: JMPR EQ,Y                                                                                                                                                             |                                                        |       |       |       |         |                      |                       |     |

| 5                                                                                                                                                                              | 31 24                                                  | 23 1  | .9 18 |       |         |                      |                       |     |

|                                                                                                                                                                                | Opcode                                                 | COND  |       | У     |         |                      |                       |     |

|                                                                                                                                                                                | 8                                                      | 5     |       | 1     | 19      | <sup>▶</sup> `` Off: | set                   |     |

| www.akademi.itu.edu.tr/e                                                                                                                                                       | in/buzluca                                             |       |       |       |         |                      | 005-2022 Feza BUZLUCA | B.8 |

|                                                                          | Usag                       | ge of Berkeley    | RISC I Instructions                                                                                                  |  |  |

|--------------------------------------------------------------------------|----------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

| quanti                                                                   | ty. By using regist        | er RO, which alwo | used in any field to specify a zero<br>ays contains 0's (zeros), it is possible<br>a constant into another register. |  |  |

| ADD                                                                      | R0, R21, R22               | R22←R21           | (Move)                                                                                                               |  |  |

| ADD                                                                      | R0, #150, R22              | R22←150           | (Immediate load)                                                                                                     |  |  |

| ADD                                                                      | R22, #1, R22               | R22←R22 +1        | (Increment)                                                                                                          |  |  |

| The load and store instructions move data between a register and memory. |                            |                   |                                                                                                                      |  |  |

| LDL                                                                      | (R22)#150,R5               | R5←M[R22 +1       | 50] Load long: 32-bit data transfer                                                                                  |  |  |

| LDL                                                                      | (R22)#0,R5                 | R5←M[R22]         |                                                                                                                      |  |  |

| LDL                                                                      | (R0)#500,R5                | R5←M[500]         |                                                                                                                      |  |  |

|                                                                          |                            |                   |                                                                                                                      |  |  |

|                                                                          |                            |                   |                                                                                                                      |  |  |

|                                                                          | lami itu adu tulan kunluan |                   |                                                                                                                      |  |  |

|                                                                          | lemi.itu.edu.tr/en/buzluca |                   |                                                                                                                      |  |  |

| Computer Architecture                                           |            |                            |                  |  |  |

|-----------------------------------------------------------------|------------|----------------------------|------------------|--|--|

| Data transfer instructions:                                     |            |                            |                  |  |  |

| <u>Opcode</u>                                                   | Operands   | Register Transfer          | Description      |  |  |

| LDL                                                             | (Rs)S2,Rd  | $Rd \leftarrow M[Rs + S2]$ | Long load        |  |  |

| LDSU                                                            | (Rs)S2,Rd  | $Rd \leftarrow M[Rs + S2]$ | Short unsigned   |  |  |

| LDSS                                                            | (Rs)S2,Rd  | $Rd \leftarrow M[Rs + S2]$ | Short signed     |  |  |

| LDBU                                                            | (Rs)S2,Rd  | $Rd \leftarrow M[Rs + S2]$ | Byte unsigned    |  |  |

| LDBS                                                            | (Rs)S2,Rd  | $Rd \leftarrow M[Rs + S2]$ | Byte signed      |  |  |

| LDHI                                                            | Y,Rd       | $Rd \leftarrow Y$          | Immediate high   |  |  |

| STL                                                             | (Rs)S2, Rm | $M[Rs + S2] \leftarrow Rm$ | Store load       |  |  |

| STS                                                             | (Rs)S2, Rm |                            |                  |  |  |

| STB                                                             | (Rs)S2, Rm |                            |                  |  |  |

| GETPSW                                                          | Rd         | Rd ← PSW                   | Load status word |  |  |

| PUTPSW                                                          | Rd         | $PSW \leftarrow Rd$        | Set status word  |  |  |

| www.akademi.itu.edu.tr/en/buzluca © 2005-2022 Feza BUZLUCA B.11 |            |                            |                  |  |  |

| Computer Architecture                                                                                                                                                                                                                                                                                                        |               |                                                                                                  |                                 |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|

| Program control instructions:                                                                                                                                                                                                                                                                                                |               |                                                                                                  |                                 |  |  |  |

| <u>Opcode</u>                                                                                                                                                                                                                                                                                                                | Operands      | Register Transfer                                                                                | Description                     |  |  |  |

| JMP                                                                                                                                                                                                                                                                                                                          | COND,S2(Rs)   | $PC \leftarrow Rs + S2$                                                                          | Absolute (direct) addressing    |  |  |  |

| JMPR                                                                                                                                                                                                                                                                                                                         | COND,Y        | $PC \leftarrow PC + Y$                                                                           | Relative                        |  |  |  |

| CALL                                                                                                                                                                                                                                                                                                                         | S2(Rs),Rd     | Rd ← PC<br>PC ← Rs + S2<br>☆ CWP ← CWP -1                                                        | Current window pointer          |  |  |  |

| CALLR                                                                                                                                                                                                                                                                                                                        | Y,Rd          | Rd ← PC<br>PC ← PC + Y<br>CWP ← CWP -1                                                           | Relative                        |  |  |  |

| RET                                                                                                                                                                                                                                                                                                                          | (Rd)S2        | $\textit{PC} \leftarrow \textit{Rd} + \textit{S2}$<br>$\textit{CWP} \leftarrow \textit{CWP} + 1$ |                                 |  |  |  |

| In the Berkeley RISC I processor, every time the program calls a new procedure,<br>the current window pointer (CWP) is decremented by one to point to the next-<br>lower register window.<br>Thus, the main program (process A) uses the registers with the highest numbers<br>(R116-R137) and the global registers (R0-R9). |               |                                                                                                  |                                 |  |  |  |

| www.akademi.itu.edu.                                                                                                                                                                                                                                                                                                         | tr/en/buzluca |                                                                                                  | © 2005-2022 Feza BLIZELICA B.12 |  |  |  |

| Computer Architecture                                                                                                             |                           |                                            |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------|--|--|--|--|

| Exemplary Pro                                                                                                                     | ogram:                    |                                            |  |  |  |  |

|                                                                                                                                   |                           | symbolic instructions (passing parameters  |  |  |  |  |

| over overlapping register windows) to: <ul> <li>add two 32-bit signed numbers located in memory slots 500 and 504, and</li> </ul> |                           |                                            |  |  |  |  |

|                                                                                                                                   | esult to memory slot 508. | in memory stors 500 and 507, and           |  |  |  |  |

|                                                                                                                                   |                           | s after the address stored in register R1. |  |  |  |  |

| Solution:                                                                                                                         | Program                   | Explanation                                |  |  |  |  |

|                                                                                                                                   |                           | R10 ← M[500] (1st parameter)               |  |  |  |  |

|                                                                                                                                   | LDL (R0) #504, R11        |                                            |  |  |  |  |

|                                                                                                                                   | CALL (R1)#20, R15         | R15 ← PC                                   |  |  |  |  |

|                                                                                                                                   |                           | PC ← (R1)+20                               |  |  |  |  |

|                                                                                                                                   |                           | $CWP \leftarrow CWP-1$                     |  |  |  |  |

|                                                                                                                                   | STL (R0) #508, R12        | M[508] ← R12 (returned value)              |  |  |  |  |

|                                                                                                                                   |                           |                                            |  |  |  |  |

| [(R1)+20]                                                                                                                         | <br>ADD R26, R27, R28     | R28 ← R27+R26                              |  |  |  |  |

| [(,.=-]                                                                                                                           | RET (R31)#0               | PC ← (R31)+0                               |  |  |  |  |

|                                                                                                                                   |                           | CWP ← CWP+1                                |  |  |  |  |

| <b>Note:</b> When writing this program, problems that arise in the pipeline explained in Ch. 2 were not taken into consideration. |                           |                                            |  |  |  |  |

| www.akademi.itu.edu<br>www.buzluca.info                                                                                           | tr/en/buzluca             | © 2005-2022 Feza BUZLUCA B.13              |  |  |  |  |