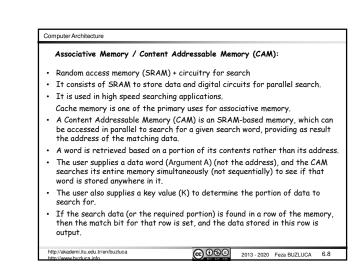

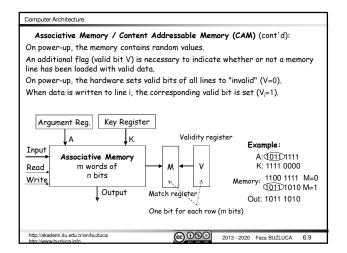

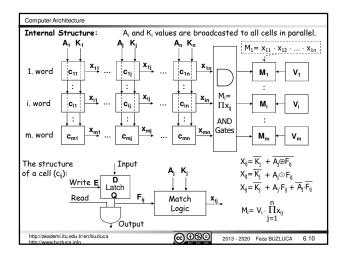

| Computer Architecture                                                                                                                                                                              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6.2 The principle of locality (Locality of reference):                                                                                                                                             |  |

| Programs tend to reuse instructions and data they have used recently.                                                                                                                              |  |

| Observation: A typical program spends 90% of its execution time in only 10% of the code.                                                                                                           |  |

| We can predict what instructions and data a program will use in the near future based on its access in the recent past.                                                                            |  |

| There are two types of locality:                                                                                                                                                                   |  |

| <b>Temporal Locality</b> (Locality in time): Recently accessed addresses are likely to be accessed in the near future.                                                                             |  |

| Spatial Locality (Locality in space) : After an access to a memory address the<br>next access will be likely to a nearby address.                                                                  |  |

| Reasons for locality:                                                                                                                                                                              |  |

| Structure of the program: The execution of instructions follows a sequential order. Program segments, such as routines and macros, tend to be stored in the same neighborhood of the memory space. |  |

| In addition, related data is stored in nearby locations.                                                                                                                                           |  |

| Loops                                                                                                                                                                                              |  |

| Arrays                                                                                                                                                                                             |  |

| http://akademi.itu.edu.tr/en/buzluca<br>http://www.huzluca.info                                                                                                                                    |  |

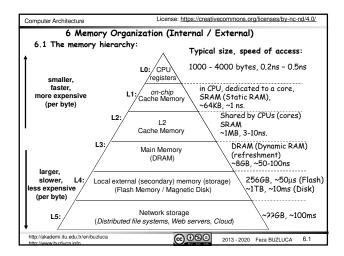

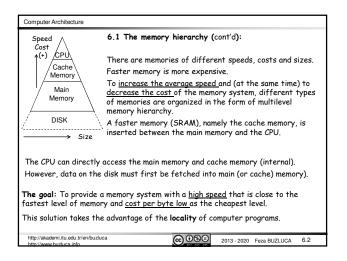

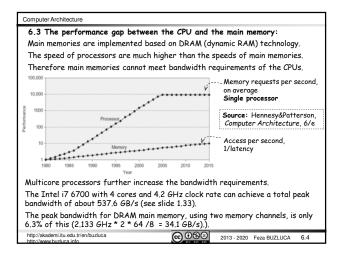

## Computer Architecture 6.4 Memory Technologies RAM (Random-Access Memory): Actually, referring to only this type of memory as "random access" is a misuse of the term because all of the semiconductor (electronic) memories used in computer systems are random access (not sequential). Distinguishing characteristic of RAM: CPU can access the memory to read data and to write new data directly (easily and rapidly without an additional device). These operations are accomplished through the use of electrical signals. It would be more precise to call this type of memory as "Read-Write Memory". • RAM is volatile. If the power is interrupted, then the data are lost. Thus, RAM can be used only as temporary storage. Memory latency measures: Access time: Time between write/read request and when desired word has been stored or made available for use Cycle time: Minimum time between two unrelated requests to memory There are two types of RAM; DRAM (Dynamic RAM) and SRAM (Static RAM). http://akademi.itu.edu.tr/en/buzluca 2013 - 2020 Feza BUZLUCA 6.5

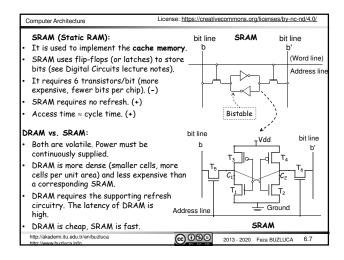

|    | DRAM (Dynamic RAM):                                                                                                                                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | It is used to implement the main memory.                                                                                                               |

| •  | A dynamic RAM (DRAM) is made with cells that Address line store data as charge on capacitors.                                                          |

| •  | Because capacitors have a natural tendency to<br>discharge, dynamic RAMs require periodic charge<br>refreshing to maintain data storage (~ every 8ms). |

| •  | The stored charge leaks away, even with power<br>continuously applied (The term dynamic refers to Bit line (Data) Ground this tendency ).              |

|    | During the refresh process, the memory is unavailable (latency). (-)                                                                                   |

|    | Must be re-written after being read. Reading destroys the information (latency)                                                                        |

|    | Difference between access time and cycle time. Cycle time > access time (-)                                                                            |

|    | Cheap and dense: one transistor/bit. More bits can be placed on one chip. (+)                                                                          |

| 50 | ome improvements:                                                                                                                                      |

|    | SDRAM (Synchronous DRAM): Added clock to DRAM interface. Burst mode.                                                                                   |

|    | DDRAM (Double data rate DRAM): Data is transferred on both the rising edge and falling edge.                                                           |

|    | http://akademi.itu.edu.tr/en/buzluca 6.6                                                                                                               |

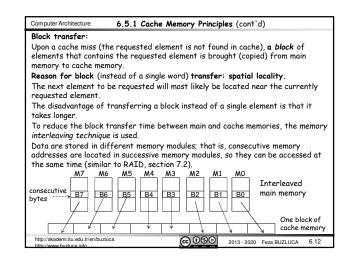

## Computer Architecture 6.5 Cache Memory , The internal memory system 6.5.1 Cache Memory Principles The goal is to store copies of frequently accessed data in the fast cache memory to reduce the average access time. Hit: The requested word is found in cache memory. Miss: A miss occurs if the requested data is not found in cache memory. Address Example For read operations only: Cache memory access time: 20 ns. Main memory access time: 100 ns. Hit/ Cache Miss Memory Main Hit ratio: H=0.9 (90% hit) Memory System Average memory access time: $t_a = 0.9*20 + 0.1*100 = 28 \text{ ns.}$ CPU Data In systems with asynchronous bus operations like the MC68000, the DTACK Multiplexer sianal is sent to the CPU at different times based on there being a hit or not. Thus, when data is retrieved from cache memory, the bus cycle is completed Data faste http://akademi.itu.edu.tr/en/buzl ©®® 2013 - 2020 Feza BUZLUCA 6.11

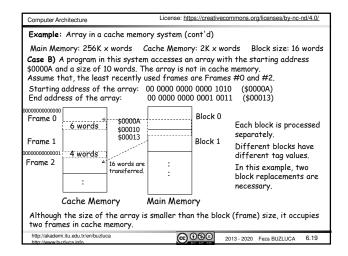

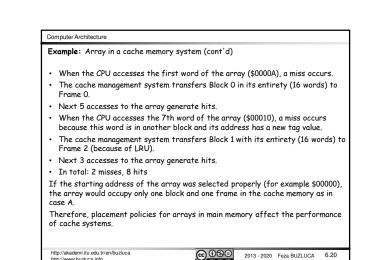

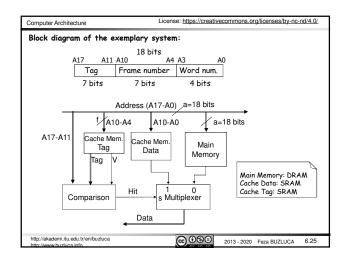

| Computer Architecture License: <u>https://creativecommons.org/licenses/by-nc-nd/4.0/</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

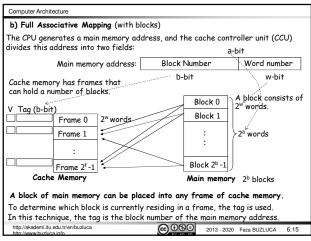

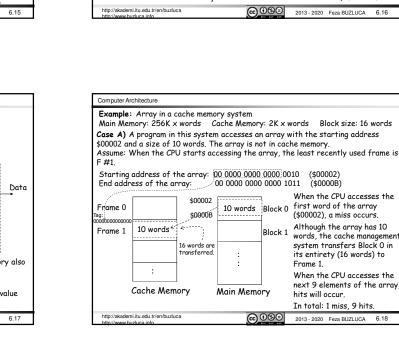

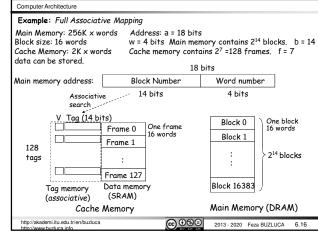

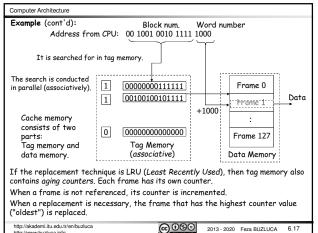

| <ul> <li>6.5.1 Cache Memory Principles (cont'd)</li> <li>Replacement Techniques:</li> <li>The capacity of cache memory is lower than that of main memory.</li> <li>At any moment, only a part of the data in main memory can be kept in cache memory.</li> <li>When cache memory is full, a replacement algorithm is needed to determine which block in cache will be replaced by the new block from main memory.</li> <li>There are different replacement techniques; the most common ones are:</li> <li>FIFO (<i>First In, First Out</i>): The block that has been in the cache the longest is replaced.</li> <li>LRU (<i>Least Recently Used</i>): The block that has been used the least while residing in the cache is replaced.</li> <li>The access history of each block is taken into consideration.</li> <li>An aging counter is assigned to each block to keep track of references to that block in cache.</li> </ul> | <ul> <li>6.5.2 Cache Memory Mapping Techniques</li> <li>Is a content of main memory currently present in cache memory?</li> <li>If present, where in cache memory is the data located?</li> <li>1. Full Associative Mapping <ul> <li>a) Without blocks:</li> <li>In practice, all mapping techniques operate on data blocks.</li> <li>For the sake of simplicity, we will first look at a technique that does not use blocks</li> </ul> </li> <li>Method: The most frequently referenced addresses and their data are kept in an associative memory. <ul> <li>Valid</li> <li>Address Data</li> <li>Cache Memory:</li> <li>Address Data</li> <li>Cache Memory:</li> <li>Address Data</li> <li>Cache Memory:</li> <li>Address Data</li> <li>AD001 02</li> <li>Hit</li> <li>A001 3A</li> <li>OCC0 54</li> <li>OH00 AL</li> <li>Address Data</li> </ul> </li> </ul> |

| A hardware unit, called the Cache Memory Controller or Cache Memory<br>Management Unit, performs cache operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Without blocks, the technique benefits from only temporal locality but not spatial locality.<br>Therefore, in practice, data blocks are moved between main and cache memories.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| http://akademi.itu.edu.tr/en/buziuca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | http://akademi.itu.edu.tr/en/buzluca                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

6.18

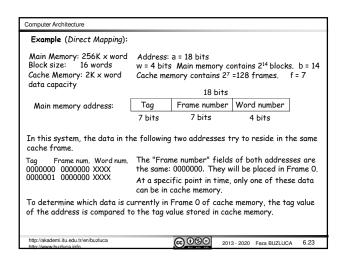

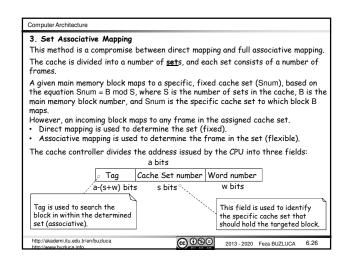

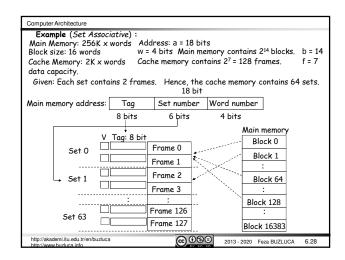

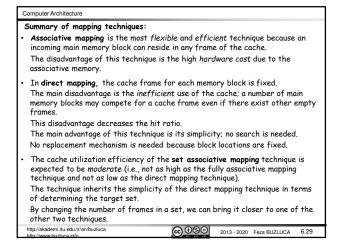

| 2. Direct Mapping                                                                                                                                                                                                                                                                                                                         |                                                                                                                          |                      |               |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|--|

| An incoming main memory bl<br>location.                                                                                                                                                                                                                                                                                                   | lock is always placed in <sup>.</sup>                                                                                    | to a specific, fixed | cache frame   |  |

| It is not necessary to search for the location of a block in the cache because it is<br>predetermined and fixed.                                                                                                                                                                                                                          |                                                                                                                          |                      |               |  |

| Therefore, associative mem                                                                                                                                                                                                                                                                                                                | iory is not necessary.                                                                                                   |                      |               |  |

|                                                                                                                                                                                                                                                                                                                                           | As the size of main memory is greater than that of the cache, several blocks of main memory map to the same cache frame. |                      |               |  |

| It is necessary to determin<br>frame.                                                                                                                                                                                                                                                                                                     | e which main memory b                                                                                                    | lock is currently re | esiding in a  |  |

| The cache memory control ur                                                                                                                                                                                                                                                                                                               | nit divides the address                                                                                                  | from the CPU into    | three fields: |  |

| a bits                                                                                                                                                                                                                                                                                                                                    |                                                                                                                          |                      |               |  |

| ,≏ Tag                                                                                                                                                                                                                                                                                                                                    | Cache Frame number                                                                                                       | Word number          |               |  |

| a-(f+w) bits f bits • w bits                                                                                                                                                                                                                                                                                                              |                                                                                                                          |                      |               |  |

| It indicates which of the<br>blocks that can be placed<br>in this frame is currently<br>in cache.<br>This field determines the number of the cache frame that<br>will hold this data.<br>The blocks that have this filed in common (same) try to<br>reside in the same frame.<br>Only one of them can reside in the cache any given momen |                                                                                                                          |                      | ume) try to   |  |

<u>@08</u>0

2013 - 2020 Feza BUZLUCA 6.21

Computer Architecture

http://akademi.itu.edu.tr/en/buzluca

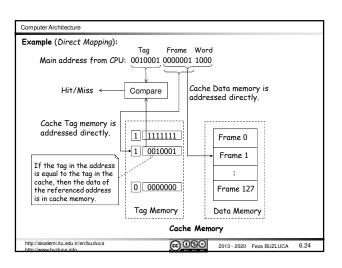

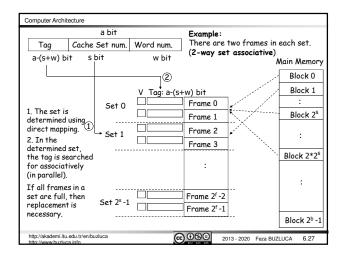

| Computer Arc          | a bit                  |                                                         |                                           |

|-----------------------|------------------------|---------------------------------------------------------|-------------------------------------------|

| T                     |                        | num. Word num.                                          |                                           |

| Tag                   |                        |                                                         | Main memory                               |

| a-(f+w) bi            | t fbit                 | w bit                                                   | 2 <sup>b</sup> blocks                     |

|                       | V T                    | ag: a-(f+w) bit                                         | Block 0 One bloc                          |

| <b>T</b> 1 ( )        |                        | Frame 0                                                 | Block 1                                   |

| The fram<br>determine | e IS<br>ed directly.   | Frame 1                                                 |                                           |

| i = B mod             | F                      | :                                                       | Block 2 <sup>f</sup>                      |

| i : Frame nu          | umber                  | Frame 2 <sup>f</sup> -1                                 | :                                         |

| B: Block nu           | mber                   |                                                         | Block 2 <sup>b</sup> -1                   |

| F: Number             | of frames              | F=2 <sup>f</sup> frames                                 |                                           |

| F=2 <sup>f</sup>      |                        |                                                         |                                           |

|                       |                        | n only reside in the cache<br>Ne Frame number" filed of | frame with the number that is the address |

|                       |                        |                                                         | iche, two blocks with the same            |

|                       |                        | field cannot be in the cach                             |                                           |

|                       |                        | cision algorithm is not ne                              |                                           |

|                       |                        | ncoming block is fixed, th                              |                                           |

| Association<br>cache. | ve memory is r         | not necessary because the                               | ere is no need to search in the           |

|                       | .itu.edu.tr/en/buzluca | @ 080                                                   | 2013 - 2020 Feza BUZLUCA 6.22             |

| Computer Architecture                                                                                   |           |

|---------------------------------------------------------------------------------------------------------|-----------|

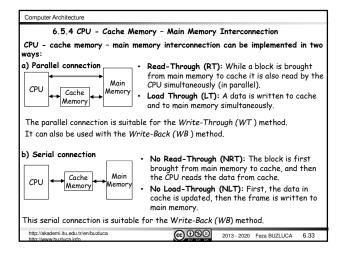

| 6.5.3 Cache Memory - Main Memory Interactions                                                           |           |

| → Read (Hit): Data is read from cache memory.                                                           |           |

| → Read (Miss):                                                                                          |           |

| a) Read-Through (RT):                                                                                   |           |

| While the data (block) is being brought from main memory to cache, i<br>read by the CPU simultaneously. | t is also |

| Cache memory and main memory are accessed in parallel.                                                  |           |

| b) No Read-Through (NRT):                                                                               |           |

| Data are first brought from main memory to cache memory, and then reads data from the cache.            | the CPU   |

| $\rightarrow$ Write (Hit):                                                                              |           |

| a) Write-Through (WT):                                                                                  |           |

| In each write operation, data is written to cache and also to main mer                                  | nory.     |

| Disadvantage: It increases the access time.                                                             |           |

| Advantage: It provides coherence between the cache frames and the<br>counterparts in main memory.       | ir        |

| http://skademi.itu.edu.tr/en/buzbuca                                                                    | A 6.30    |

| Computer Architecture License: https://creativecommons.org/licenses/by-nc-nd/4.0/                                                                                                                                       | Computer Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| → Write (Hit) (cont'd):                                                                                                                                                                                                 | $\rightarrow$ Write (Miss):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| b) Write-Back (WB):                                                                                                                                                                                                     | a) Write Allocate (WA):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Writes are done only to the cache.                                                                                                                                                                                      | The main memory block is updated and brought to cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A block is written back to main memory only when a replacement is needed.                                                                                                                                               | a) No Write Allocate (NWA):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| There are two types of write-back policies: Simple write-back and flagged write-back.                                                                                                                                   | The missed main memory block is updated in main memory and not brought to<br>cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>Simple Write-Back (SWB):</li> <li>The replaced frame is always written back to main memory.</li> </ul>                                                                                                         | If an attempt is made to read this block later, a miss will occur, and data will<br>be brought to cache.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| It is not checked whether the frame was changed or not.                                                                                                                                                                 | The write-through (WT) policy can be used together with write-allocate (WA) or no-write-allocate (NWA) methods. WTWA, WTNWA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>Flagged Write-Back (FWB):</li> <li>Every cache frame is assigned a bit, called the dirty bit, to indicate that at<br/>least one write operation has been made to the block while residing in cache.</li> </ul> | In write-back (WB) policy, to maintain coherence between cache and main memory at the beginning, the write-allocate (WA) method is used (WBWA).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| At replacement time, the dirty bit is checked: if it is set, then the block is                                                                                                                                          | Information held in Tag memory:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| written back to main memory; otherwise, it is simply overwritten by the<br>incoming block.                                                                                                                              | In addition to Valid (V) and tag bits, depending on the method used, the following data must be also kept in tag memory:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| The dirty bit is stored in the tag memory of the cache.                                                                                                                                                                 | <ul> <li>If LRU is used aging counters,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                 | <ul> <li>If flagged Write-Back (FWB) method is used "dirty" bit (D).</li> <li>A single line of a tag memory: V D Counter Tag</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| http://akademi.itu.edu.tr/en/buzluca COSO 2013 - 2020 Feza BUZLUCA 6.31                                                                                                                                                 | http://akademi.itu.edu.tr/en.buziuca colored c |

| Computer Archite                                                         | cture                    |                                       |                                         |                                                 |

|--------------------------------------------------------------------------|--------------------------|---------------------------------------|-----------------------------------------|-------------------------------------------------|

| 6.5.5 Acces                                                              | s Time:                  |                                       |                                         |                                                 |

| t <sub>a</sub> : Average Memory Access Time                              |                          |                                       |                                         |                                                 |

| W: Write ratio (number of write accesses / total number of all accesses) |                          |                                       |                                         |                                                 |

| h : Hit ratio                                                            |                          |                                       |                                         |                                                 |

| t <sub>cache</sub> : Cache                                               | e memory o               | iccess time                           |                                         |                                                 |

| t <sub>main</sub> : Main                                                 | memory ac                | cess time                             |                                         |                                                 |

| t <sub>trans</sub> : Time                                                | to transfe               | r a block betwee                      | en main memory and                      | d cache                                         |

| Wd: The p                                                                | probability              | that a block in a                     | cache is updated                        |                                                 |

|                                                                          | WT, RT/LT WB,WA, NRT/NLT |                                       |                                         |                                                 |

| (Write-through , Parallel read/write)                                    |                          | (Write-back, Serial read/write)       |                                         |                                                 |

| Probability                                                              | NWA                      | WA                                    | SWB                                     | FWB                                             |

| Read Hit                                                                 |                          | s Time                                | Access                                  |                                                 |

| (1-w)h                                                                   | t <sub>cache</sub>       | t <sub>cache</sub>                    | t <sub>cache</sub>                      | t <sub>cache</sub>                              |

| Read Miss                                                                |                          |                                       |                                         | Wd (2t <sub>trans</sub> +t <sub>cache</sub> ) + |

| (1-w)(1-h)                                                               | t <sub>trans</sub>       | t <sub>trans</sub>                    | 2t <sub>trans</sub> +t <sub>cache</sub> | $(1-w_d)(t_{trans}+t_{cache})$                  |

| Write Hit                                                                |                          |                                       |                                         |                                                 |

| wh                                                                       | t <sub>main</sub>        | t <sub>main</sub>                     | t <sub>cache</sub>                      | t <sub>cache</sub>                              |

| Write Miss                                                               |                          |                                       |                                         | Wd (2t <sub>trans</sub> +t <sub>cache</sub> ) + |

| w(1-h)                                                                   | t <sub>main</sub>        | t <sub>main</sub> +t <sub>trans</sub> | 2t <sub>trans</sub> +t <sub>cache</sub> | $(1-w_d)(t_{trans}+t_{cache})$                  |

| http://akademi.itu.e                                                     |                          |                                       | 2013                                    | - 2020 Feza BUZLUCA 6.34                        |

| Com              | puter Architecture                                                                                                                                                                                    |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acc              | cess Time Calculation:                                                                                                                                                                                |

| • Wr             | rite Through with Write Allocate, Read/Load Through (WTWA, RT/LT):<br>Read Hit + Read Miss + Write Hit + Write Miss                                                                                   |

| t <sub>a</sub> = | $(1-w)h t_{cache} + (1-w)(1-h)t_{trans} + w \cdot h \cdot t_{main} + w(1-h)(t_{main} + t_{trans})$                                                                                                    |

| t <sub>a</sub> = | $(1 - w)h t_{cache} + (1 - h)t_{trans} + w t_{main}$                                                                                                                                                  |

| • Wr             | rite Through with No Write Allocate, Read/Load Through (WTNWA,RT/LT)                                                                                                                                  |

| ta =             | $(1 - w)h t_{cache} + (1-w)(1-h)t_{trans} + w \cdot h \cdot t_{main} + w(1-h)t_{main}$                                                                                                                |

| t <sub>a</sub> = | $(1 - w)h t_{cache} + (1 - w)(1 - h)t_{trans} + w t_{main}$                                                                                                                                           |

| ·Sim             | ple Write Back with Write Allocate, No Read Through (SWBWA, NRT/NLT)<br>Read Hit + Read Miss +Write Hit + Write Miss                                                                                  |

|                  | $ \begin{array}{c} (1 - w)h \ t_{cache} + (1 - w)(1 - h)(2t_{rrans} + \ t_{cache}) + \ w \ h \ t_{cache} + \ w(1 - h)(2t_{rrans} + \ t_{cache}) \\ + \ t_{cache} + (1 - h) \ 2t_{rrans} \end{array} $ |

|                  | $t_{\text{trans}}$ is needed to transfer a frame from cache to main memory and the second is needed to bring the new block from main memory to cache.                                                 |

| ·Flag            | gged Write Back,Write Allocate, No Read Through (FWBWA,NRT/NLT):                                                                                                                                      |

|                  | $t_a = t_{cache} + (1 - h)t_{trans} + w_d (1 - h)t_{trans}$                                                                                                                                           |

|                  | $t_a = t_{cache} + (1 - h)(1 + w_d)t_{trans}$                                                                                                                                                         |

|                  | ://akademi.itu.edu.tr/en/buzluca COSE 2013 - 2020 Feza BUZLUCA 6.35                                                                                                                                   |

| Exemplary processors with co                                    | iche memories:       |                            |      |

|-----------------------------------------------------------------|----------------------|----------------------------|------|

| Intel386™: Cache memory is a                                    | outside of the CPU c | hip. SRAM memory.          |      |

| <b>Intel486™ (1989)</b><br>8-KByte on-chip (L1)                 |                      |                            |      |

| Intel® Pentium® (1993)                                          |                      |                            |      |

| L1 on-chip: 8 KB instruction, 8                                 | KB data cache (Har   | vard architecture)         |      |

| Intel P6 Family: (1995-1999)                                    |                      |                            |      |

| - Intel Pentium Pro:                                            |                      |                            |      |

| L1 on-chip: 8 KB instruction,                                   |                      | rvard architecture)        |      |

| First L2 cache memory in the                                    |                      |                            |      |

| L2 on-chip: 256 KB. Different                                   | interconnections be  | etween L1,L2 and the       | CPU. |

| - Intel Pentium II:                                             |                      |                            |      |

| L1 on-chip: 16 KB instruction,<br>L2 on-chip: 256 KB, 512 KB, 1 |                      | larvard architecture)      |      |

| · Intel® Pentium® M (2003)                                      |                      |                            |      |

| L1 on-chip: 32 KB instruction,                                  | 32 KB data cache     |                            |      |

| L2 on-chip: up to 2 MByte                                       |                      |                            |      |

| Intel® Core™ i9-9900 (2019                                      | )                    |                            |      |

| Multicore: 8 cores. Private cad                                 |                      | l shared caches (L2: 2     | MiB) |

| L3: 16 MiB smartcache: All cor                                  | es share this cache. |                            |      |

| http://akademi.itu.edu.tr/en/buzluca                            | 0000                 | 2013 - 2020 Eeza BUZI LICA | 6.36 |