License: https://creativecommons.org/licenses/by-nc-nd/4.0/

## 4. Interrupt

## Hardware interrupt:

If a predefined event occurs in an external device (for example I/O interface), this device issues an interrupt request to the CPU.

## Design Issues:

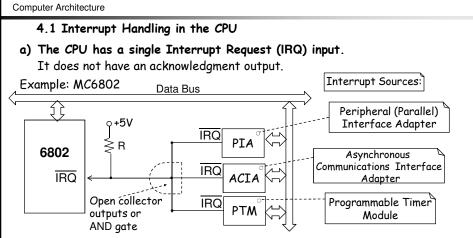

- Source: There may be multiple interrupt sources. How does the processor determine which device issued the interrupt request?

- Priority: In case of simultaneous, multiple interrupt requests, how does the processor decide which one to process?

- Start address of the ISR: If the processor accepts the interrupt request of a device, how does it determine the starting address of the interrupt service routine (ISR) (or interrupt handler) related to the requesting device?

- · Autovectored

- Vectored

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.1

- The source of the interrupt is identified by polling at the beginning of the ISR.

- The order in which the interrupt sources are polled determines their priorities.

- To make the source device remove its interrupt request (acknowledgment), a software action is necessary (reading the port of the source, writing to the control register, etc.).

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

- b) The CPU has an Interrupt Request (INT) input and an Interrupt Acknowledge (INTA) output. The CPU uses vectored interrupts.

- Interrupt sources are connected to the CPU over an interrupt priority controller.

- In the event of multiple interrupt requests, the controller decides which device gets the acknowledgment signal (INTA).

- The source device that receives the INTA places a word (vector number VN) on the data bus.

- The CPU indexes into the interrupt vector table using this vector number and obtains the starting address of the associated ISR.

Computer Architecture

# 4.2 Vector Address:

The CPU keeps the information about the interrupt handlers in a **vector table**. This table is used to associate an interrupt request with a specific ISR.

There are two different methods for storing this information in the vector table:

1. The table contains the starting addresses of the ISRs.

The interrupt source gives the CPU an index to table in the form of the vector number.

Using this index, the CPU accesses an entry in the table, gets the starting address of the ISR, and writes it to the program counter (PC). Example: MC 68000.

2. The table contains executable code, namely the ISR itself.

In practice, an interrupt handler cannot be stored entirely inside the interrupt vector table.

Therefore, the code at each entry is "JMP ISR\_address", where ISR\_address is the address of the interrupt service routine.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

## Vectored and Autovectored interrupts:

Vectored interrupt technique: The external interrupt source (for example I/O interface) supplies its vector address to the processor.

**Autovectored interrupt technique:** The external device does not supply the vector number in response to the interrupt acknowledge.

Each interrupt input (or level) of the processor has a fixed and predetermined vector number (a specific row in the vector table).

For example, in 6802 different interrupts (NMI, IRQ, SWI) have their own rows in the table.

NMI: Non-maskable interrupt; IRQ: Interrupt request; SWI: Software interrupt The processor "knows" where to find the address of the ISR if an interrupt is

issued to the NMI pin.

Example:

Vector table of the 6802

Since the 6802 has an address bus of 16 bits, each starting address occupies two 8-bit memory locations.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info **FFFF** Starting address of RESET **FFFE** the reset program. **FFFD** NMI + **FFFC** Starting addresses of **FFFB** SWI 5 the interrupt service **FFFA** programs. FFF9 IRQ\* FFF8

© © © © 2013-2021 Feza BUZLUCA

| Computer Architecture                | Vectors Numbers |         | Address |     |         |                                       | i        |  |

|--------------------------------------|-----------------|---------|---------|-----|---------|---------------------------------------|----------|--|

|                                      | Hex             | Decimal | Dec     | Hex | Space 6 | Assignment                            |          |  |

| Interrupt Vector Table               | 0               | 0       | 0       | 000 | SP      | Reset: Initial SSP <sup>2</sup>       |          |  |

| of the MC 68000:                     | 1               | 1       | 4       | 004 | SP      | Reset: Initial PC <sup>2</sup>        | ]        |  |

|                                      | 2               | 2       | 8       | 800 | SD      | Bus Error                             |          |  |

|                                      | 3               | 3       | 12      | 00C | SD      | Address Error                         | i        |  |

| TI 44.00.000 : .                     | 4               | 4       | 16      | 010 | SD      | Illegal Instruction                   | i        |  |

| The MC68000 is                       | 5               | 5       | 20      | 014 | SD      | Zero Divide                           | i        |  |

| capable of handling                  | 6               | 6       | 24      | 018 | SD      | CHK Instruction                       | i        |  |

|                                      | 7               | 7       | 28      | 01C | SD      | TRAPV Instruction                     | l        |  |

| both vectored and                    | 8               | 8       | 32      | 020 | SD      | Privilege Violation                   | i        |  |

| autovectored                         | 9               | 9       | 36      | 024 | SD      | Trace                                 | l        |  |

| interrupts.                          | A               | 10      | 40      | 028 | SD      | Line 1010 Emulator                    |          |  |

|                                      | В               | 11      | 44      | 02C | SD      | Line 1111 Emulator                    |          |  |

|                                      | С               | 121     | 48      | 030 | SD      | (Unassigned, Reserved)                |          |  |

|                                      | D               | 131     | 52      | 034 | SD      | (Unassigned, Reserved)                |          |  |

|                                      | Ε               | 14      | 56      | 038 | SD      | Format Error 5                        | l        |  |

|                                      | F               | 15      | 60      | 03C | SD      | Uninitialized Interrupt Vector        | ı        |  |

|                                      | 10-17           | 16-231  | 64      | 040 | SD      | (Unassigned, Reserved)                | ı        |  |

|                                      |                 | l .     | 92      | 05C |         | _                                     | ı        |  |

|                                      | 18              | 24      | 96      | 060 | SD      | Spurious Interrupt <sup>3</sup>       | l        |  |

|                                      | 19              | 25      | 100     | 064 | SD      | Level 1 Interrupt Autovector          | ı        |  |

|                                      | 1A              | 26      | 104     | 890 | SD      | Level 2 Interrupt Autovector          | ı        |  |

|                                      | 1B              | 27      | 108     | 06C | SD      | Level 3 Interrupt Autovector          | 1        |  |

|                                      | 1C              | 28      | 112     | 070 | SD      | Level 4 Interrupt Autovector          | ı        |  |

|                                      | 1D              | 29      | 116     | 074 | SD      | Level 5 Interrupt Autovector          | ı        |  |

|                                      | 1E              | 30      | 120     | 078 | SD      | Level 6 Interrupt Autovector          | ı        |  |

|                                      | 1F              | 31      | 124     | 07C | SD      | Level 7 Interrupt Autovector          |          |  |

|                                      | 20-2F           | 32-47   | 128     | 080 | SD      | TRAP Instruction Vectors <sup>4</sup> | i        |  |

|                                      |                 |         | 188     | 0BC |         | _                                     | i        |  |

|                                      | 30-3F           | 48-631  | 192     | 000 | SD      | (Unassigned, Reserved)                | l        |  |

|                                      |                 |         | 255     | OFF |         | _                                     | <u> </u> |  |

| http://akademi.itu.edu.tr/en/buzluca | 40-FF           | 64-255  | 256     | 100 | SD      | User Interrupt Vectors                | 104 4.6  |  |

| http://www.buzluca.info              |                 |         | 1020    | 3FC |         | -                                     | JCA 4.6  |  |

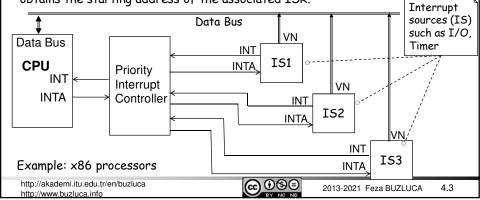

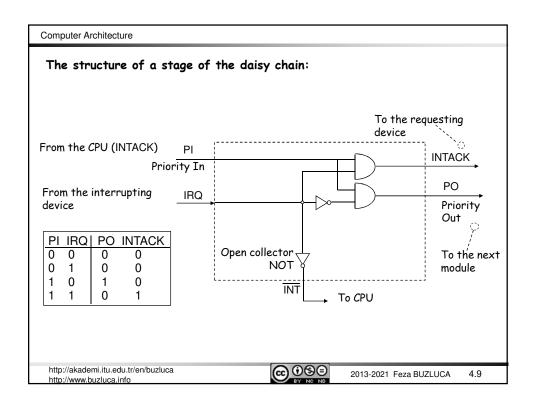

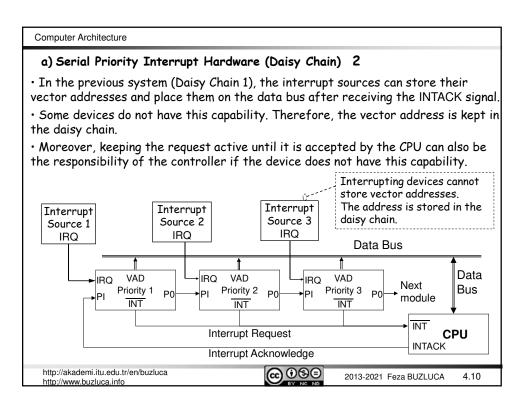

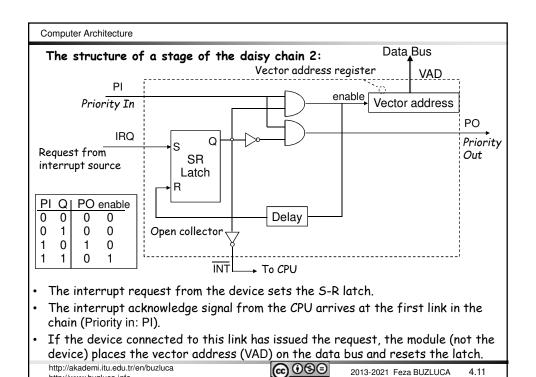

# How the priority chain works:

- The interrupt acknowledge line is daisy chained through the modules.

- · When the CPU accepts an interrupt, it sends out an interrupt acknowledge.

- The interrupt acknowledge signal from the CPU arrives at the first link in the chain (Priority in: PI).

- a. If the device connected to this link has issued the request,

- 1. The module sends the INTACK signal to its device (interrupt source).

- The device (interrupt source) puts its vector address (VAD) on the data bus.

- 3. The module negates (deactivates) its PO (Priority out) so that the next module cannot get the acknowledge signal.

- b. If the device connected to this link has not issued the request,

- The module asserts (activates) its PO (Priority out) so that the next module gets the right to check the request and supply the vector address.

- This mechanism is also called hardware poll.

- If the request of a device is accepted, this device deactivates its IRQ output.

- The device keeps its request (IRQ) active until it gets the acknowledgment.

**@ ⊕ ⊕**

9 2013-2021 Feza BUZLUCA

4 8

http://www.buzluca.info

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

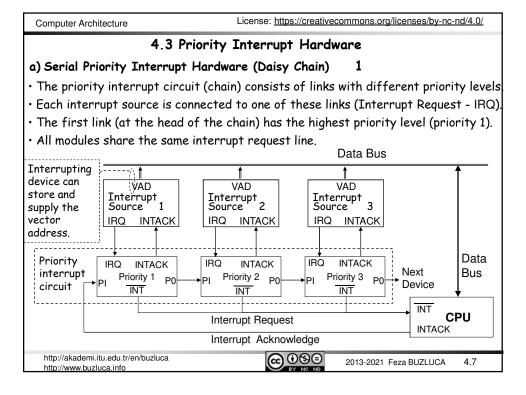

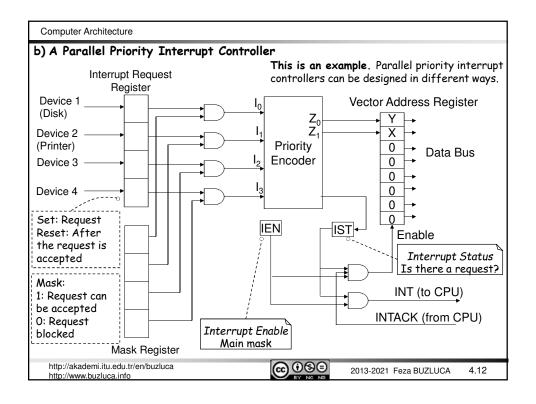

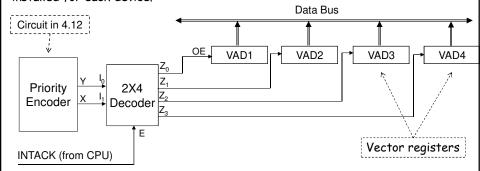

Vector addresses of the devices in this system:

Device 1: 0000 0000

Priorities:

Device 2: 0000 0001

Device 1 > Device 2 > Device 3 > Device 4

Device 3: 0000 0010

Device 4: 0000 0011

# Truth table of the priority encoder:

|                | Input          | ts             | Outputs        |                           |                           |     |

|----------------|----------------|----------------|----------------|---------------------------|---------------------------|-----|

| I <sub>o</sub> | I <sub>1</sub> | l <sub>2</sub> | l <sub>3</sub> | <b>X</b> = Z <sub>1</sub> | <b>Y</b> = Z <sub>0</sub> | IST |

| 1              | х              | х              | х              | 0                         | 0                         | 1   |

| 0              | 1              | х              | х              | 0                         | 1                         | 1   |

| 0              | 0              | 1              | х              | 1                         | 0                         | 1   |

| 0              | 0              | 0              | 1              | 1                         | 1                         | 1   |

| 0              | 0              | 0              | 0              | Φ                         | Φ                         | 0   |

# Logical expressions:

$$X = Z_1 = I_0' I_1'$$

$Y = Z_0 = I_0' I_1 + I_0' I_2'$

$(IST) = I_0 + I_1 + I_2 + I_3$

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info © (1) (S) (E) (N) (N) (N)

2013-2021 Feza BUZLUCA

4.13

# Computer Architecture

In the exemplary system (4.12), the vector addresses of the devices are predetermined and fixed (Device 1 (Disk): 0000 0000).

To make the system more flexible, a separate vector address register can be installed for each device.

When the interrupt request of a device is accepted, the OE (Output enable) pin of the related register is activated.

Vector address registers are installed in the system so that the CPU can write to them

Vector address registers can be initialized (or modified) by system programs.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info **@ ⊕ ⊕**

2013-2021 Feza BUZLUCA

# 4.4 Interrupt Processing: Necessary actions before and after the ISR Before the ISR:

Reminder: The CPU checks the interrupt requests after the execution cycle.

If a request is accepted, the CPU enters the interrupt cycle (Slide 1.18).

In the interrupt cycle, the following actions are performed by the CPU.

These actions are internal operations of the CPU; they are not performed by a program.

$SP \leftarrow SP-1$ Stack pointer is decremented (depending on address length: 1, 2, 4)

$\begin{array}{ll} \text{M[SP]} \leftarrow \text{PC} & \text{Return address saved on stack} \\ \text{INTACK} \leftarrow 1 & \text{Interrupt acknowledge} \end{array} \\ \begin{array}{ll} \text{Start address of the ISR} \end{array}$

$PC \leftarrow VAD$ PC ← Vector address or PC ← Table [Vnum.] (from Vector table)

$SP \leftarrow SP-1$

$M[SP] \leftarrow SR \quad \text{Status register (SR) saved on stack}$

$IEN \leftarrow 0$ Other interrupts are masked (disabled). This bit is in SR (Status reg.)

In the next fetch cycle, the CPU continues with the first instruction of the ISR because the PC includes its starting address (PC  $\leftarrow$  VAD).

Some CPUs also push internal registers to the stack. Some CPUs leave this job to the programmer.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.15

Computer Architecture

#### Returning from the ISR:

Reminder: The Interrupt service routines are terminated by a special instruction: "return from interrupt" (RTI).

This instruction performs the following necessary operations to return from the ISR to the previously interrupted program.

$SR \leftarrow M[SP]$ Status register from stack (Remember IEN is in SR)

$SP \leftarrow SP+1$ Stack pointer is incremented (depending on the length of SR: 1, 2)

$PC \leftarrow M[SP]$ Return address

$SP \leftarrow SP+1$ Stack pointer is incremented (depending on address length: 1, 2, 4)

(If internal registers were also pushed to the stack automatically in the interrupt cycle, they are pulled by the RTI.)

Note that the CPU enters the interrupt cycle only before starting the ISR. Returning operations are performed by the last instruction (RTI) of the ISR.

#### Conclusion:

Interrupt processing operations are time-consuming (many memory accesses). Therefore, frequent interrupt requests can degrade the performance of a system. For example, interrupt-driven I/O is not suitable for applications where I/O operations are performed very frequently (e.g., file transfer).

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

## Example: Interrupt-driven I/O

### Problem:

The instruction cycle of a CPU has the following 5 states (cycles) with the given durations:

- 1. Instruction fetch: 60 ns, 2. Instruction decode: 20 ns, 3. Operand fetch: 60 ns,

- 4. Execution: 30 ns, 5. Interrupt: 200 ns. 5.

Housekeeping operations in the interrupt cycle (saving the return address, reading the vector address, etc.) take 200 ns.---

The interrupt-driven I/O technique is used to transfer 10 words from the I/O interface to the memory.

The interrupt service program takes 500 ns (housekeeping operations in the interrupt cycle are not included) and transfers one word each time.

Assume that we start a clock (Time = 0) when the CPU begins to run the program.

The first interrupt request arrives from the I/O interface when the CPU is in the instruction fetch cycle for the first instruction (Time = 5ns).

- ${f a}$ . When (Time =?) can the first word be transferred from the I/O interface to the memory? Why?

- **b.** When (Time = ?) will all 10 words be transferred if the I/O interface is always ready to transfer?

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.17

Computer Architecture

## Example: Interrupt-driven I/O (cont'd)

#### Solution:

Remember: Interrupt requests are checked after the execution of the instruction. If there is a request and interrupts are enabled, the CPU enters the interrupt cycle.

The data is transferred in the ISR (Interrupt Service Routine).

RTI and related operations are included in the ISR.

a. First word:

Fetch + Decode + Operand + Execute + Housekeeping + ISR Time = 60 + 20 + 60 + 30 + 200 + 500 = 870ns

**b**. 10 words:

One word is transferred in each ISR.

After the ISR, the CPU returns to the main program, runs one instruction, and enters the ISR again.

Time =  $10 \times 870 = 8700$ ns (Time-consuming. Overhead is large.)

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

# 4.5 Exceptions

Exceptions are situations that are caused either by programming errors or by anomalous conditions.

In these cases, the processor stops executing the current code, begins running an **exception handling routine**, and then returns to the normal program flow.

Example: Exceptions in MC68000

#### External:

- Reset

- · Bus Error (BERR)

- · Interrupts: vectored, autovectored

#### Internal

- Trace: If T bit in SR is "1", programs run step-by-step (for debugging).

- · Address error : Word/long access attempt to odd addresses

- Software interrupt (TRAP 0 -15), TRAPV (Trap on overflow), CHK

- · Illegal instruction: The opcode does not exist.

- Instruction emulation (Instruction starting with \$A=1010 and \$F=1111)

- Privilege violation: Some instructions are only available in supervisor mode.

- Divide by zero

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.19

#### Computer Architecture

# When the 68000 receives an exception, the following procedure is performed:

- SR  $\rightarrow$  Temp (A copy of the Status Register SR is created.)

- S $\leftarrow$ 1, T $\leftarrow$ 0 (The CPU switches to supervisor mode. Trace is disabled.)

- The PC (return address) is saved on the supervisor stack.

- The copy of SR in Temp (S and T have their original values) is saved on the supervisor stack using the SSP (supervisor stack pointer).

- The address of the exception handler is obtained from the vector table.

- Data and address registers are not saved on the stack by the 68000.

It is up to the programmer of the service routine to save only the used registers on the stack.

## Returning from the exception:

- The programmer must pull saved values (if there are any) from the stack.

- Service routines must end with the instruction RTE (Return from Exception). During the execution of the instruction RTE

- The status register SR is pulled from the stack.

- The return address is pulled from the stack.

In the case of RESET, not all of these operations are performed.

In some exceptions (BERR, interrupts) some additional operations are performed.

http://akademi.itu.edu.tr/en/buzluca

2013-2021 Feza BUZLUCA

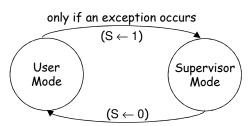

# 4.5.1 Privilege Modes

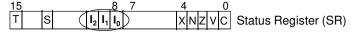

The 68K operates in one of two levels of privilege: the *supervisor* mode or the *user* mode.

The privilege mode determines which operations (instructions) are legal.

The mode is also indicated by the FCO (Function Codes Output) pins of the processor and optionally used by an external memory management circuit to control the accesses to certain memory locations (or devices) (Slides 3.23-24).

The mode is also used to choose between the supervisor stack pointer (SSP) and the user stack pointer (USP) in instruction references.

## Supervisor mode:

The supervisor mode has the higher level of privilege.

The mode of the processor is determined by the S bit of the status register (S=1). All instructions can be executed in the supervisor mode.

#### User mode:

If the S bit of the status register is clear, the processor is in the user mode. Most instructions execute identically in either mode. However, some instructions having important system effects are privileged (e.g., STOP, RESET).

To ensure that a user program cannot enter the supervisor mode except in a controlled manner, the instructions that modify the entire status register are privileged.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info @ 0 0 0 0

2013-2021 Feza BUZLUCA

1 21

Computer Architecture

## Transition between privilege modes

When the processor is in the user mode, only exception processing can change the privilege mode.

Remember, during exception processing, the current state of the S bit of the status register is saved, and the S bit is set  $(S \leftarrow 1)$ , putting the processor in the supervisor mode.

Therefore, exception service programs run in supervisor mode.

If the exception occurred in the user mode, after the exception handler, the processor switches to user mode again because the RTE instruction pulls the original value of the SR (that includes the S bit) from the stack.

The transition from supervisor to user mode can also be accomplished by the instructions that can modify the status register SR, such as MOVE to SR, ANDI to SR, and EORI to SR.

RTE (pulls the SR from the stack) or instructions that modify the SR: MOVE, ANDI, EORI

http://akademi.itu.edu.tr/en/buzluca

**©** 080

2013-2021 Feza BUZLUCA

4 22

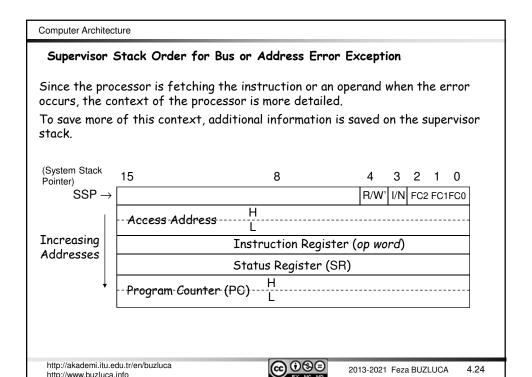

## 4.5.2 Bus Error (BERR) and Address Error:

A bus error exception occurs when the external logic asserts the BERR' (active low) input of the 68000. See slide 3.19 Avoiding Infinite Waiting.

An address error exception occurs when the processor attempts to access a word (16-bit) or long word (32-bit) operand or an instruction at an odd address.

An address error is similar to an internally generated bus error.

Unlike interrupts, the current bus cycle is aborted.

The current instruction is not finished (even the bus cycle is not completed).

The current processor activity, whether instruction or exception processing, is terminated, and the processor immediately begins exception processing. Exception processing for a bus error/address error follows the usual sequence of steps.

However, additional information is saved on the supervisor stack.

If a bus error occurs during the exception processing for a bus error, an address error, or a reset, the processor halts and isolates itself from the system bus (high impedance).

This halt simplifies the detection of a system failure and protects memory contents from erroneous accesses.

Only an external RESET operation can restart a halted processor.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

License: https://creativecommons.org/licenses/by-nc-nd/4.0/

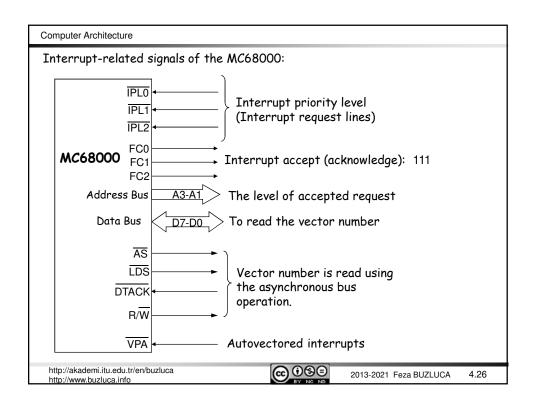

# 4.5.3 Interrupts in MC68000:

The 68000 has three interrupt request input-lines (IPL2, IPL1, IPL0).

The 3-bit value at these inputs indicates the level (1-7) of the interrupt request. All lines negated indicates no interrupt request.

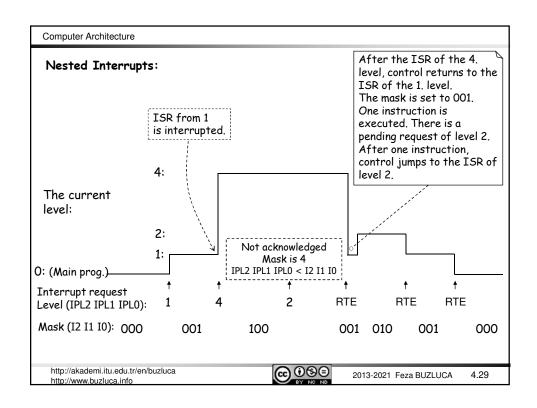

If the priority level of the pending interrupt is greater than the current processor priority (interrupt masks), the request is accepted, and the exception processing sequence is started.

Interrupt Mask ( $I_0 I_1 I_2$ )

IPL2, IPL1, IPL0 > 12, 11, 10 interrupt is accepted.

IPL2, IPL1, IPL0  $\leq$  12, 11, 10 interrupt is not accepted, execution continues with the next instruction.

Priority level 7 is a special case. Level 7 interrupts cannot be inhibited by the interrupt priority mask.

Level 7 provides a "nonmaskable interrupt" capability.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

## When the 68000 accepts an interrupt request:

- SR  $\rightarrow$  Temp (a copy of SR is created.)

- S←1, T←0

- The PC (return address) is saved on the supervisor stack.

- The copy of SR in Temp (where S and T have their original values) is saved on the stack.

- 12, 11, 10 ← IPL2, IPL1, IPL0 The level of the interrupt being acknowledged is (Mask ← Interrupt Level) written to the masks. Hence, interrupt requests with lower or equal levels are disabled.

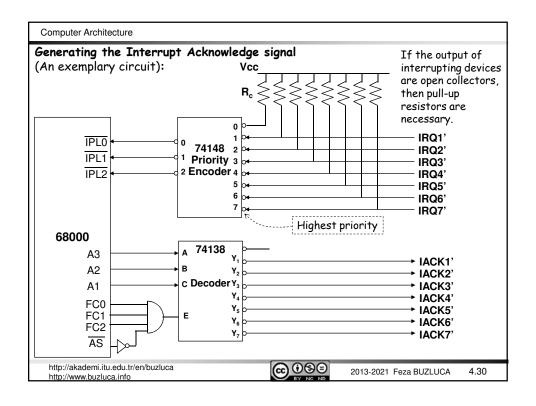

- FC2, FC1, FC0 ← 111 (Interrupt Acknowledge)

- A3, A2, A1 ← The level of the interrupt being acknowledged.

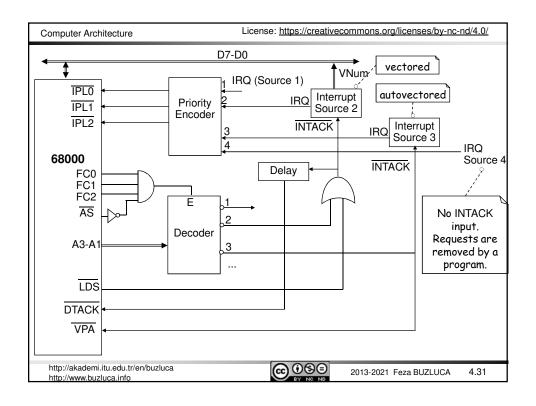

## a) Vectored interrupts:

- The interrupting device places a vector number on the data bus and asserts DTACK' to acknowledge the cycle.

- The 68000 reads the 8-bit vector number on the data bus lines D7-D0.

- The vector number provides the number of the row of the vector table where the starting address of the interrupt service routine is placed.

- As each row of the table is 4 bytes long, to calculate the address of the row, the vector number is multiplied by 4 (see the table in 4.6).

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

1 27

Computer Architecture

# When the 68000 accepts an interrupt request (cont'd):

## b) Autovectored interrupts:

- If the interrupting device asserts VPA' instead of DTACK', it means that this device will (can) not supply a vector number.

- In this case, the 68000 obtains the starting address of the interrupt service routine from predetermined and fixed rows of the vector table.

- Each autovectored interrupt level has its own entry in the table: rows 25 -31 (see 4.6).

# Responsibilities of the programmer:

- Registers that are used in the interrupt service routine must be saved on the stack.

- Before returning, the same registers must be pulled from stack.

- For these stack operations the MOVEM (move multiple) instruction can be used.

- If necessary, the programmer of the ISR can change the value of the interrupt masks. (Remember that the ISR runs in supervisor mode.)

- Hence, the programmer can enable interrupts with lower levels or disable interrupts with higher levels (except level 7).

- At the end of the ISR, there must be an RTE (Return from Exception)

instruction.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

# 4.5.4 Software Interrupts

In the MC68000, there are 16 software interrupts, which are called traps: TRAP #0 - TRAP #15

These instructions generate internal interrupts and start exception processing. Each TRAP has its own entry (rows 32-47) in the vector table (slide 4.6).

What is the difference between procedure calls (CALL, JSR instructions) and software interrupts (TRAP instructions)?

Exception service programs of TRAP instructions run in supervisor mode.

System programmers write necessary system programs (for example, for using system resources, such as the PIA) and install them as exception service routines in the system.

The authors of the user programs can call these routines to access the system resources (for example, I/O units) by executing the TRAP instructions.

Since exception service programs run in supervisor mode, using these routines, the user can access some system resources in a controlled manner.

Normally, a user may not write directly to a register of the PIA (if it is protected in user mode), but using a service routine, the user can send data over the PIA.

Software interrupts are also used to return from user programs to the operating system.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info 2013-2021 Feza BUZLUCA

## 4.5.5 Instruction Emulation (Unimplemented instructions)

In the instruction set of the MC68000, there are no instructions (in machine language) starting with \$A (1010) or \$F (1111).

Opcodes starting with bit patterns equaling 1010 (Line A) and 1111 (Line F) are distinguished as **unimplemented instructions**, and separate exception vectors are assigned to these patterns to permit efficient emulation.

System designers (system programmers) can create their own instructions that start with these opcodes and place them in a program with other instructions.

When the 68000 fetches such an instruction and tries to decode it, it discovers that the instruction is unimplemented and starts exception processing.

The exception service routine related to the instruction is written by the system programmer. This routine performs the required operation.

The address in PC that is saved on the stack as a return address before starting the exception's service routine is the address of the unimplemented instruction.

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.33

Computer Architecture

## Example:

In a MC68000-based system, using the instruction emulation capability, the following instructions will be implemented.

• ADD.B address1, address2, address3 (address3)←(address1)+(address2)

This instruction adds two 8-bit integers in address1 and address2, then writes the result to address3. Addresses are 32 bits.

• ADD.W address1, address2, address3 (address3) ← (address1) + (address2) This instruction performs the same operation on **16**-bit integers.

## Solution:

First, the structure (format) of the instructions  $\,$  must be defined. An exemplary structure:

ADD.B address1,address2,address3 \$F000 address1,address2,address3 ADD.W address1,address2,address3 \$F001 address1,address2,address3

The last bit of the operation word (Op word) is used to indicate the size. 0:B , 1:W

ADD.B: 1111 0000 0000 0000 = \$F000 ----ADD.W: 1111 0000 0000 0001 = \$F001

http://akademi.itu.edu.tr/en/buzluca http://www.buzluca.info

2013-2021 Feza BUZLUCA

4.34

ADD.B:

-address1

-address2-

address3

-> F000

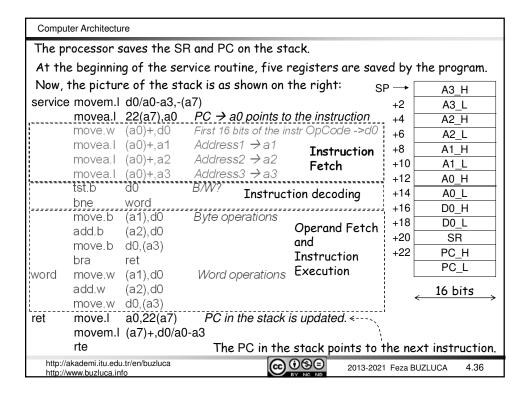

Computer Architecture We must write an exception service routine that performs the desired operations for the instructions. Before we write the service routine, we can implement a main program that can be used to test the service routine: main lea stack,a7 // Stack pointer initial address adda.l #40,a7 // Stack grows downward move.l #service,(\$2C) <-----// Service routine starting address to table \$f000,0,\$1000,0,\$1100,0,\$1200 //ADD.B \$1000,\$1100,\$1200 dc.w dc.w \$f001,0,\$2000,0,\$2100,0,\$2200 //ADD.W \$2000,\$2100,\$2200 \$500 org stack ds.b 40 // Memory allocation for stack The vector address of the Line F exception is (\$2C) in the vector table (11th row). The starting address of the service routine must be written to this entry. Remember that at the beginning of the service routine, the used registers must be saved on the stack. Which registers must be saved can be only determined after the service program is completely written. service movem.l d0/a0-a3,-(a7) // D0, A0, A1, A2, A3 to stack <u>@</u> ⊕ http://akademi.itu.edu.tr/en/buzluca 2013-2021 Feza BUZLUCA http://www.buzluca.info