Computer Architecture

#### Appendix A: MC 68000

The 68K will be used to illustrate some topics discussed in class.

- 16-bit data bus (can operate in 8-bit mode when necessary)

- 16/32-bit microprocessor

- Internally 32-bit data paths and instructions, but interfaces with external components using a 16-bit data bus, so, a programmer considers it 32-bit chip while a system designer considers it a 16-bit chip)

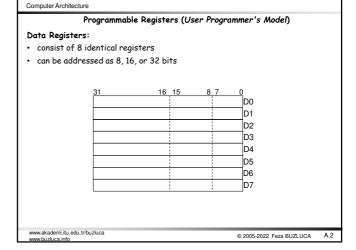

- 16 32-bit registers (eight data and eight address registers)

- 24-bit address bus: These 24 lines can therefore address 16 MB of physical memory with byte resolution

- Operations can be performed on 5 different data types:

- Bit, byte, 16-bits (word), 32 bits (long word), BCD

- Memory-mapped input/output (I/O)

- · 14 addressing modes

- Two modes of operation: Supervisor vs. User

- o Some instructions cannot be executed in user mode

- Access to memory can be restricted by connecting the FCO (functions code output) pins to the memory address decoding circuitry.

wakademi itu edu tr/buzluca

© 2005-2022 Feza BUZLUCA

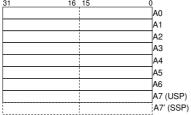

#### Computer Architecture Address Registers

- 8+1 registers (A0 to A7 and A7'). These are typically used as pointers.

- The address registers can only be used as 16 or 32 bits.

- The A7 register is also the stack pointer. It is duplicated for the user and supervisor states, i.e, A7 (User Stack Pointer -USP) and A7' (System Stack Pointer -USP).

Since the address bus is 24 bits wide, only the first 24 bits of the data in an address register is used.

When the low-order word (16 bits) in an address register is used, these bits are sign-extended to 24 bits before being placed on the address bus.

.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA

#### Computer Architecture

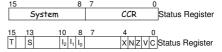

### Status Register:

- · Consists of two parts: System and user (CCR Condition Code Register)

- Condition codes: Overflow (V), Zero (Z), Negative (N), Carry (C), Extend (X).

- Interrupt mask ( $I_0 I_1 I_2$ )

- Additional status bits indicating that the processor is in Trace (T) mode

- and/or in the Supervisor (5) state

Bits 5, 6, 7, 11, 12, 14 are undefined and reserved for future expansion.

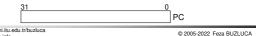

# Program Counter (PC):

- 32 bits

- Can also be used as an address register

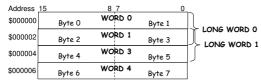

# Data Organization in Memory

High-order parts of data are placed in memory starting from lower addresses..

- Bytes are individually addressable.

- The high-order byte of a word has the same address as the word.

- The low-order byte has an odd address, one count higher.

- Instructions and multibyte data are accessed only on word (even byte)

- Each word (16 bits) or long word (32 bits) must start at even address.

- If a long-word operand is located at address n (n even), then the second word of that operand is located at address n+2.

akademi itu edu tr/buzluca © 2005-2022 Feza BUZLUCA

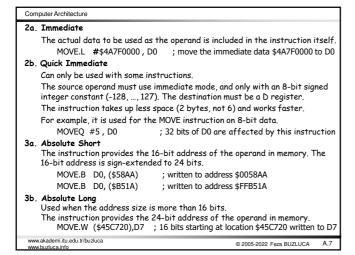

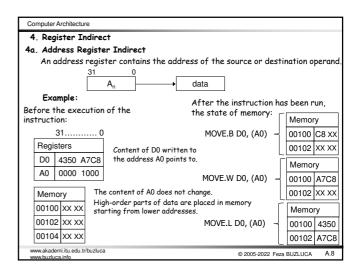

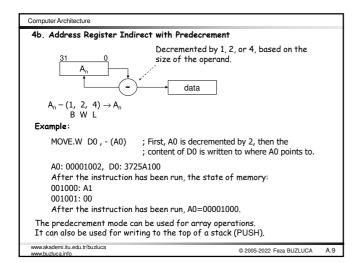

### Addressing Modes

The 68000 supports 14 different addressing modes derived from six basic types:

- 1. Register Direct

- 2. Immediate

- 3. Absolute

- 4. Register Indirect

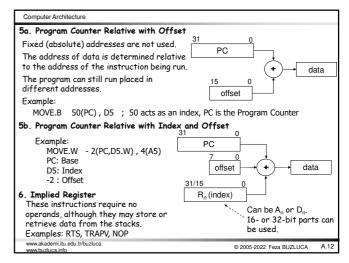

- 5. Program Counter Relative

- Implied

# 1a. Data Register Direct

The operand is in a data register (whose name is given directly).

$D_n \to D_m\,$ MOVE.W  $D_n$ ,  $D_m$ B: Byte, W: Word, L: Long

# 1b. Address Register Direct

The operand is in an address register (whose name is given directly).

If the destination is an address register, the instruction ends with an "A."

MOVEA.W D1, A5  $D_1 \rightarrow A_5$  (Source data register, dest. addr. register) The data may only be W: Word or L: Long.

zakademi itu edu tr/buzluca

© 2005-2022 Feza BUZLUCA

A.4

Computer Architecture MC68000 Instructions In this section, we will introduce some MC68000 instructions. Data Movement Instructions: Move multiple registers Writes all specified registers to memory starting at a specific address, or reads data from specified memory address and places them in specified registers. Syntax 1: MOVEM <register list>,<ea>

Syntax 2: MOVEM <ea>,<register list> Examples: MOVEM.L D0-D7/A0-A6 , \$1234 ; save D0-D7/A0-A6 to ; memory starting at \$1234 MOVEM.L (A5), D0/D5/A0-A3 ; read D0, D5, A0-A3, ; from memory address pointed by A5 Can be used to save working registers on entry to a subroutine and to restore them at the end of a subroutine. MOVEM.L D0-D5/A0-A3,-(A7) ; Push registers D0-D5/A0-A3 onto the stack Body of subroutine MOVEM.L (A7)+,D0-D5/A0-A3 ; Restore registers D0-D5/A0-A3 from the stack RTS Return to the calling program wakademi itu edu tr/buzluca © 2005-2022 Feza BUZLUCA

Computer Architecture LEA Load effective address Operation:  $[An] \leftarrow \langle ea \rangle$ Used to copy the address of a variable into an address register. All 32 bits of the address register are affected by this instruction. ; register A0 will point to the Sample syntax: LEA Table,A0 beginning of Table calculates effective address of Table w.r.t. to PC, deposits it in A0. LEA (Table,PC),A0 LEA (-6,A0,D0.L),A6 calculates A0+D0.L sign-extended ; to 32 bits minus 6, deposits it in A6. LEA (Table,PC,D0),A6 Example: ARRAY, A0 ; Array address to A0 MOVE.B (A0)+, D1 : Load first element of array to D1, increment A0 to point to next elmt. ARRAY DS.B 100 ; Define Storage (directive) w.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.19

Computer Architecture Flow Control Instructions: Bcc Branch on condition cc cc specifies the condition. If cc = 1 THEN [PC]  $\leftarrow$  [PC] + d d: 8- or 16-bit signed offset. Reminder: When the instruction is being run, PC points to the instruction after Bcc. Syntax: Bcc < label > Relative size can be specified if needed: BEQ.B (EQual) or BNE.W (Not Equal) If the size is not specified, the compiler computes the relative address of an appropriate size based on the distance of the label. Conditions (cc): BCC branch on carry clear branch if C = 0BEQ branch on equal branch if Z=1 BGT branch if  $(Z + (N \oplus V)) = 0$ branch on greater than branch if (C + Z) = 0BHI branch on higher than **BGE** branch on greater than or equal branch if  $(N \oplus V) = 0$ BIT branch on less than branch if  $(N \oplus V) = 1$ BLS branch on lower than or same branch if (C + Z) = 1v akademi itu edu tr/buzluca © 2005-2022 Feza BUZLUCA

Computer Architecture Setting of Flags Overflow:  $V = C_7 \oplus C_8$ 8 / 8 C<sub>s</sub>: Carry C7: Carry in the previous bit 8-hit ALU Overflow can also be determined based on  $\begin{array}{c} \mathsf{pos} + \mathsf{pos} \ \to \mathsf{neg} \\ \mathsf{neg} + \mathsf{neg} \ \to \mathsf{pos} \end{array}$  $pos - neg \rightarrow neg$   $neg - pos \rightarrow pos$ CSZV In subtraction and comparison operations, the carry C bit serves as the BORROW flag. Result

first number is smaller than the second.

In subtraction using two's complement, if an (n+1)st bit forms, there is no borrow.

Reminder: Carry: May result from the addition of  $\underline{\text{unsigned}}$  numbers. Indicates that the result does not fit into n bits and an (n+1)st bit is needed. Borrow: May result from the subtraction of  $\underline{\textbf{unsigned}}$  numbers. Indicates that the Overflow: May form only in the addition or subtraction of <u>signed</u> numbers.

Indicates that the result cannot be expressed using the allotted number of bits. .akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.21 Computer Architecture Test condition, decrement, and branch DBcc Syntax: DBcc Dn,<label> Here, the label is a 16-bit relative address. 16 bits of Dn is used as a counter. IF(condition cc false) THEN [Dn]  $\leftarrow$  [Dn] - 1 (decrement loop counter) IF [Dn] = -1 THEN instruction after DBcc (PC incremented by 2 in fetch cyc.) ELSE  $[PC] \leftarrow [PC] + d$  (branch relative) ELSE instruction after DBcc (PC incremented by 2 in fetch cycle.) Example: Loop (10 times) MOVEO #9, D0 : Start value 9, because exiting on D0=-1 ; Inside the loop DBF : Here, F: False, condition always false, D0.L1 ; branches if false demi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A.22

Example: Comparing Two Arrays (Are all elements equal?) The first array starts at address ARRAY1, the second starts at address ARRAY2. The arrays have 50 8-bit elements. The contents of the arrays have been filled in before the program starts DBcc exits ARRAY1, A0 ARRAY2, A1 LEA Start addresses of the arrays A0 points to ARRAY1, A1 points to ARRAY2 LEA MOVE.W SIZE, DO Size of arrays

Decrement D0 by 1 for use in DBNE later SUBQ.W #1. D0 СМРМ.В (A0)+, (A1)+ Array elements compared as pair of bytes DRNF DO, LOOP Test, decrement D0, and loop until not equal Why did loop exit? (D0?), sets N &Z based on D0 TST.W D0  $\operatorname{BMI}$ **EQUAL** ; Branch if neg. (If D0=-1 on exit, all elmts. equal) DIFFERENT ...... EQUAL ...... Allocate memory for elements of 1st array: 50B ARRAY1 DS.B Allocate memory for elements of 2nd array: 50B Define constant in memory of length one word ARRAY2 DS.B 50 DC.W 50 elements in each array www.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA