#### **Computer Architecture**

# Appendix A: MC 68000

# The 68K will be used to illustrate some topics discussed in class.

- 16-bit data bus (can operate in 8-bit mode when necessary)

- 16/32-bit microprocessor

Internally 32-bit data paths and instructions, but interfaces with external components using a 16-bit data bus, so, a programmer considers it 32-bit chip while a system designer considers it a 16-bit chip)

- 16 32-bit registers (eight data and eight address registers)

- 24-bit address bus: These 24 lines can therefore address 16 MB of physical memory with byte resolution

- Operations can be performed on 5 different data types:

- Bit, byte, 16-bits (word), 32 bits (long word), BCD

- Memory-mapped input/output (I/O)

- 14 addressing modes

- Two modes of operation: Supervisor vs. User

- o Some instructions cannot be executed in user mode

- o Access to memory can be restricted by connecting the FCO (functions code output) pins to the memory address decoding circuitry.

www.akademi.itu.edu.tr/buzluca

© 2005-2022 Feza BUZLUCA

Δ1

# Computer Architecture

# Programmable Registers (User Programmer's Model)

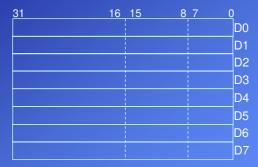

## Data Registers:

- · consist of 8 identical registers

- can be addressed as 8, 16, or 32 bits

/ww.akademi.itu.edu.tr/buzluca

ww.buzluca.info

© 2005-2022 Feza BUZLUCA

١ ٥

#### **Computer Architecture**

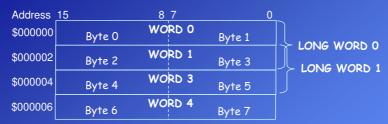

#### Data Organization in Memory

High-order parts of data are placed in memory starting from lower addresses.

- · Bytes are individually addressable.

- The high-order byte of a word has the same address as the word.

- The low-order byte has an odd address, one count higher.

- Instructions and multibyte data are accessed only on word (even byte) boundaries.

- Each word (16 bits) or long word (32 bits) must start at even address.

- If a long-word operand is located at address n (n even), then the second word of that operand is located at address n+2.

### Computer Architecture

## Addressing Modes

The 68000 supports 14 different addressing modes derived from six basic types:

- 1. Register Direct

- 2. Immediate

- 3. Absolute

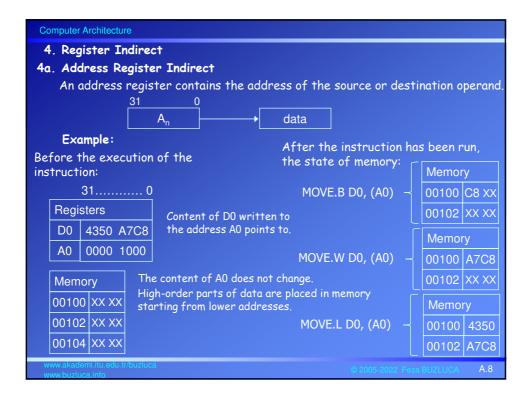

- 4. Register Indirect

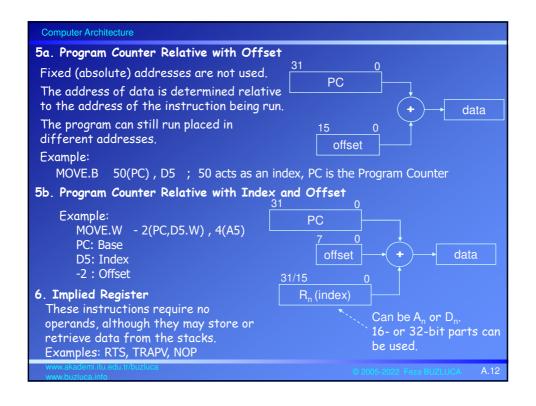

- 5. Program Counter Relative

- 6. Implied

## 1a. Data Register Direct

The operand is in a data register (whose name is given directly).

MOVE.W

$$D_n$$

,  $D_m$

$D_n \rightarrow D_m$

B: Byte, W: Word, L: Long

### 1b. Address Register Direct

The operand is in an address register (whose name is given directly).

If the destination is an address register, the instruction ends with an "A."

$\mathsf{D}_1 \to \mathsf{A}_5$  (Source data register, dest. addr. register) MOVEA.W D1, A5

The data may only be W: Word or L: Long.

### Computer Architecture 2a. Immediate The actual data to be used as the operand is included in the instruction itself. MOVE.L #\$4A7F0000 , D0 ; move the immediate data \$4A7F0000 to D0 2b. Quick Immediate Can only be used with some instructions. The source operand must use immediate mode, and only with an 8-bit signed integer constant (-128, ..., 127). The destination must be a D register. The instruction takes up less space (2 bytes, not 6) and works faster. For example, it is used for the MOVE instruction on 8-bit data. MOVEQ #5, D0 ; 32 bits of D0 are affected by this instruction 3a. Absolute Short The instruction provides the 16-bit address of the operand in memory. The 16-bit address is sign-extended to 24 bits. MOVE.B D0, (\$58AA) ; written to address \$0058AA MOVE.B D0, (\$B51A) ; written to address \$FFB51A 3b. Absolute Long Used when the address size is more than 16 bits. The instruction provides the 24-bit address of the operand in memory. MOVE.W (\$45C720),D7 ; 16 bits starting at location \$45C720 written to D7

| Computer Architecture                                                       |                                      |                                                         |

|-----------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------|

| Examples continued:                                                         |                                      |                                                         |

| CLR.L (A2)+                                                                 | 01000010 10 011 010<br>CLR L (An)+ 2 | Address register indirect postincrement                 |

| CLR.B (\$3000)                                                              | 01000010 00 111 000                  | Absolute addressing (short)                             |

|                                                                             | CLR B Absolute                       | short                                                   |

|                                                                             | 0011 0000 0000 0000                  | The address (\$3000) is in the second word.             |

| CLR.B \$4(A6)                                                               | 01000010 00 101 110                  | Address register indirect with offset                   |

|                                                                             | CLR B d(An) 6                        | The offset (\$4) is in the second word as 16 bits.      |

| CLR.B -7(A6)                                                                | 01000010 00 101 110<br>CLR B d(An) 6 | Address register indirect with offset (negative offset) |

|                                                                             | 1111 1111 1111 1001                  | The offset (-7) is in the second word as 16 bits.       |

| www.akademi.itu.edu.tr/buzluca © 2005-2022 Feza BUZLUCA A. www.buzluca.info |                                      |                                                         |

### Computer Architecture MC68000 Instructions In this section, we will introduce some MC68000 instructions. Data Movement Instructions: **MOVEM** Move multiple registers Writes all specified registers to memory starting at a specific address, or reads data from specified memory address and places them in specified registers. Syntax 1: MOVEM < register list>, < ea> Syntax 2: MOVEM <ea>,<register list> Examples: MOVEM.L D0-D7/A0-A6, \$1234; save D0-D7/A0-A6 to ; memory starting at \$1234 (A5), D0/D5/A0-A3 ; read D0, D5, A0-A3, MOVEM.L ; from memory address pointed by A5 Can be used to save working registers on entry to a subroutine and to restore them at the end of a subroutine. MOVEM.L D0-D5/A0-A3,-(A7) ; Push registers D0-D5/A0-A3 onto the stack Body of subroutine MOVEM.L (A7)+,D0-D5/A0-A3 ; Restore registers D0-D5/A0-A3 from the stack RTS ; Return to the calling program

```

LEA

Load effective address

Operation:

[An] \leftarrow <ea>

Used to copy the address of a variable into an address register.

All 32 bits of the address register are affected by this instruction.

Sample syntax: LEA Table, A0

; register A0 will point to the

; beginning of Table

LEA (Table,PC),A0

; calculates effective address of

; Table w.r.t. to PC, deposits it in A0. ; calculates A0+D0.L sign-extended

LEA (-6,A0,D0.L),A6

; to 32 bits minus 6, deposits it in A6.

LEA (Table, PC, D0), A6

Example:

; Array address to A0 ; Load first element of array to D1,

ARRAY, A0

MOVE.B (A0)+, D1

; increment A0 to point to next elmt.

ARRAY

DS.B

100

; Define Storage (directive)

```

| Computer Architecture                                                                |                                                                                |                                    |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------|--|--|

| Flow Control Instructions:                                                           |                                                                                |                                    |  |  |

| Bcc Branch on condition cc                                                           |                                                                                |                                    |  |  |

| cc specifies the condition.                                                          |                                                                                |                                    |  |  |

| If $cc = 1$ THEN [PC] $\leftarrow$ [PC] + d                                          |                                                                                |                                    |  |  |

| d: 8- or 16-bit signed offset.                                                       |                                                                                |                                    |  |  |

| Reminder: When the instruction is being run, PC points to the instruction after Bcc. |                                                                                |                                    |  |  |

| Syntax: Bcc <label></label>                                                          |                                                                                |                                    |  |  |

| Relative size can be specified if needed: BEQ.B (EQual) or BNE.W (Not Equal)         |                                                                                |                                    |  |  |

| If the size is not specified, the compiler computes the relative address of an       |                                                                                |                                    |  |  |

| appropriate size based on the distance of the label.                                 |                                                                                |                                    |  |  |

| Conditions (cc):                                                                     |                                                                                |                                    |  |  |

| BCC                                                                                  | branch on carry clear                                                          | branch if $C = 0$                  |  |  |

| BEQ                                                                                  | branch on equal                                                                | branch if Z=1                      |  |  |

| BGT                                                                                  | branch on greater than                                                         | branch if $(Z + (N \oplus V)) = 0$ |  |  |

| BHI                                                                                  | branch on higher than                                                          | branch if $(C + Z) = 0$            |  |  |

| BGE                                                                                  | branch on greater than or equal                                                | branch if $(N \oplus V) = 0$       |  |  |

| BLT                                                                                  | branch on less than                                                            | branch if $(N \oplus V) = 1$       |  |  |

| BLS                                                                                  | branch on lower than or same                                                   | branch if $(C + Z) = 1$            |  |  |

|                                                                                      | www.akademi.itu.edu.tr/buzluca www.buzluca.info  © 2005-2022 Feza BUZLUCA A.20 |                                    |  |  |

```

Computer Architecture

DBcc Test condition, decrement, and branch

Syntax: DBcc Dn, < label>

Here, the label is a 16-bit relative address.

16 bits of Dn is used as a counter.

Operation:

IF(condition cc false)

THEN [Dn] \leftarrow [Dn] - 1 (decrement loop counter)

IF [Dn] = -1 THEN instruction after DBcc (PC incremented by 2 in fetch cyc.)

Example: Loop (10 times)

; Start value 9, because exiting on D0=-1

MOVEQ #9, D0

L1

; Inside the loop

DBF

D0,L1

; Here, F: False, condition always false,

; branches if false

```

```

Computer Architecture

Example: Comparing Two Arrays (Are all elements equal?)

The first array starts at address ARRAY1, the second starts at address ARRAY2.

The arrays have 50 8-bit elements.

The contents of the arrays have been filled in before the program starts.

DBcc exits

on -1

LEA

ARRAY1, A0

; Start addresses of the arrays

LEA

ARRAY2, A1

; A0 points to ARRAY1, A1 points to ARRAY2

MOVE.W SIZE, D0

; Size of arrays

; Decrement D0 by 1 for use in DBNE later

SUBQ.W

#1, D0

; Array elements compared as pair of bytes

; Test, decrement D0, and loop until not equal

; Why did loop exit? (D0?), sets N &Z based on D0

; Branch if neg. (If D0=-1 on exit, all elmts. equal)

LOOP

CMPM.B

(A0)+, (A1)+

DBNE

D0, LOOP

TST.W

D0

EQUAL

BMI

DIFFERENT .....

EQUAL .....

ARRAY1 DS.B

; Allocate memory for elements of 1st array: 50B

50

ARRAY2 DS.B

50

; Allocate memory for elements of 2nd array: 50B

SIZE

DC.W

; Define constant in memory of length one word

; 50 elements in each array

```