Advanced Digital Circuit Design - Introduction to VHDL

Prof. Dr. Berna Örs Yalçın

Istanbul Technical University Faculty of Electrical and Electronics Engineering Department of Electronics and Communication Engineering siddika.ors@itu.edu.tr

#### Outline

- VHDL Basics

- Simulation with Test Benches

### VHDL Facts

- There are about 100 keywords (predefined lowercase identifiers) in VHDL, e.g. entity, port, architecture, process, signal, and, or, not, etc.

- -- is used for single-line comments

- Blank spaces are ignored but are not allowed in keywords, userspecified identifiers, operators or number representations.

- VHDL is case sensitive, e.g. not is not the same as NOT

## VHDL Entity Declaration

- In VHDL, an entity is a fundamental descriptive unit and the term *entity* refers to the text enclosed by the keyword pair **entity** and **end**.

- The keyword **entity** is followed by a name (for identifying the entity) **is** and a list of ports

- Identifiers are composed of alphanumeric characters and the underscore (\_\_) and are case-sensitive. They should start with an aphabetic character or underscore.

- A entity's port list is the interface between its environment and itself.

- The keywords in and out are used to denote which of the ports are inputs and which are outputs.

```

library IEEE;

1

use IEEE.STD LOGIC 1164.ALL;

2

entity simple circuit is

3

Port ( D : out STD LOGIC;

4

5

E : inout STD LOGIC;

6

A, B, C : in STD LOGIC);

7 Gend simple circuit;

8

9 Carchitecture Behavioral of simple circuit is

10

signal w1 : STD LOGIC;

11 component and gate

12

port (A, B: in STD LOGIC;

13

C: out STD LOGIC);

14 A end component;

15 Component or_gate

port (A, B: in STD LOGIC;

16

17

C: out STD LOGIC);

18 end component;

19 component not gate

port (A: in STD LOGIC;

20

21

C: out STD LOGIC);

22 Gend component;

23

begin

G1: and gate port map(A, B, w1);

24

25

G2: not_gate port map (C,E);

G3: or gate port map (E,wl,D);

26

Aend Behavioral;

```

# VHDL Entity Declaration

- Internal connections in a circuit are declared as signals using the keyword signal.

- Here a list of predefined gates (described with the keywords and\_gate, not\_gate, or\_gate) are used. Each one is an instantiation of the gate and is called a gate instance.

- Each gate instantiation has an optional name (e.g. G1, G2, G3)

- Gate output and inputs are listed in parantheses and separated by commas.

- Note the difference between entity declaration and entity instantiation. The entity simple\_circuit is declared here, but the primitive gates and\_gate, not\_gate and or\_gate are instantiated

```

1

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

2

3 Gentity simple circuit is

Port ( D : out STD LOGIC;

4

E : inout STD LOGIC;

5

A, B, C : in STD LOGIC);

7 end simple circuit;

8

9 Carchitecture Behavioral of simple circuit is

signal w1 : STD LOGIC;

10

11 component and gate

12

port (A, B: in STD LOGIC;

C: out STD LOGIC);

13

14 A end component;

15 Component or_gate

16 port (A, B: in STD LOGIC;

17

C: out STD LOGIC);

18 end component;

19 component not_gate

20

port (A: in STD LOGIC;

C: out STD LOGIC);

21

22 Gend component;

23

begin

24 G1: and_gate port map(A, B, w1);

25 G2: not gate port map (C,E);

G3: or gate port map (E,wl,D);

26

27 Gend Behavioral;

```

#### Simulation with a Test Bench

1 2

3

4

5

6

7

8

9

10

11 12

13

23 24

25

26

27 28

29

30

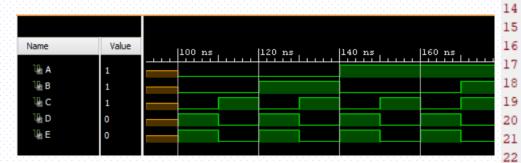

- The **process** keyword is used to start execution of a set of statements enclosed between the **begin** and **end process** keywords.

- If a statement is preceeded by a delay value (e.g., wait for 10 ns;), the simulator postpones executing the statement until the specified time has elapsed.

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

entity simple circuit tb is

end simple circuit tb;

architecture Behavioral of simple circuit tb is

component simple_circuit

Port ( D : out STD LOGIC;

E : inout STD LOGIC;

A, B, C : in STD LOGIC);

end component;

signal A, B, C, D, E : STD LOGIC;

begin

DUT: simple_circuit Port map(D,E,A,B,C);

tb: process

begin

Wait for 100 ns;

A <= '0'; B <= '0'; C <= '0';</p>

Wait for 10 ns;

0

A <= '0'; B <= '0'; C <= '1';

Wait for 10 ns;

A <= '0'; B <= '1'; C <= '0';</p>

Wait for 10 ns;

A <= '0'; B <= '1'; C <= '1';</p>

Wait for 10 ns;

A <= '1'; B <= '0'; C <= '0';</p>

Wait for 10 ns;

A <= '1'; B <= '0'; C <= '1';</p>

0

wait;

0

end process;

end Behavioral;

```

٠